# ASICデザイン

報告090125

東貴俊

# 動機

- 現在、Liquid Xenon groupでは液体キセノンを用いたTPC(Time Projection Chamber)の開発研究を行っており、PET(Positron Emission Tomography)への応用を考えている。最終的なPETにおけるPADのサイズは1mm x 1mmであり、このような多チャンネルを高速に読み出すにはプリアンプ等のフロントエンドエレクトロニクスの集積度を上げなくてはならない。同時にゲインの最適化、ノイズの最小化も計らなければならぬ。このため、フロントエンドASICの開発研究も同時に始めたこととなった。

# 目次

- 経緯

- 開発手順

- 回路説明

- 仕様パラメータの説明

- 仕様の最終決定

# 回路に必要な機能

検出器容量が大きいとアンプに電荷が読み込まれない。

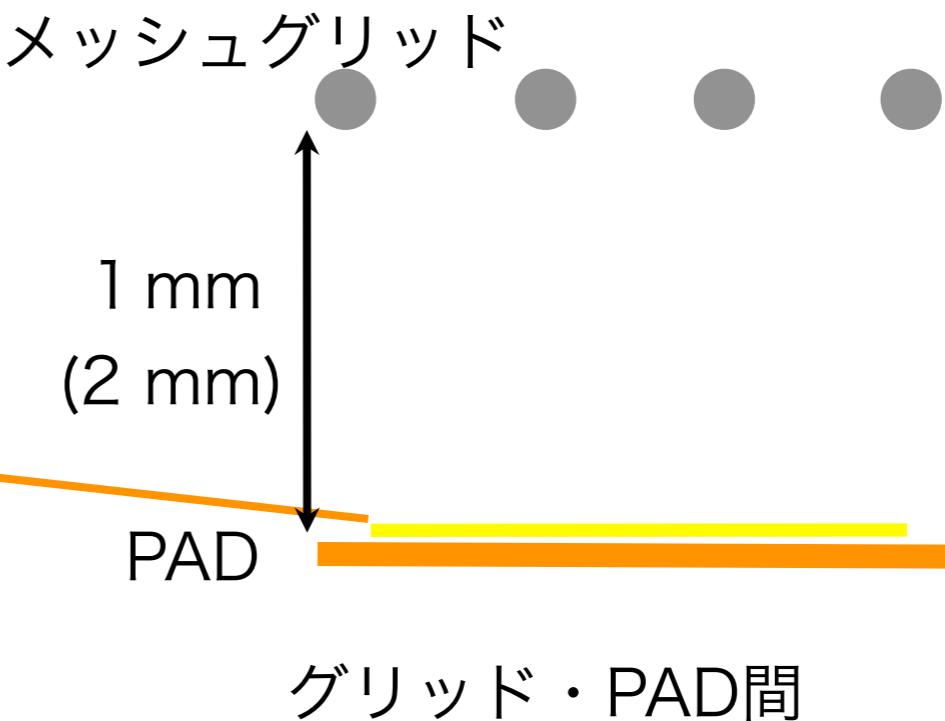

検出器容量に関しては以下のように設定した。

gridとPADの距離は2mmで、PADの大きさ

を7.5mm x 7.5mmとすると、

この静電容量は約0.25pFとなる。

検出器容量は1pF

グリッド・PAD間

1mmを2.2mm/μsでドリフト

0.45μs (2mm間では1μs)

# 回路デザイン

- ・アンプとシェイピング機能(アナログ出力)

- ・入力電荷範囲は  $1 \text{ pC}$  ( $1\text{~}5\text{fC}$ )を十分にフォローし、さらにテストパルス( $1\text{~}10\text{MeV}$ )程度の信号にもある程度の感度のあり、また、両極に対しても感度のあるもの。

- ・検出器容量 $1\text{pF}$ に対応

- ・ノイズをなるべく少なくする。

以上までの内容を踏まえて、実際にASIC回路を作成していく。

# 仕様

|                          |                     |

|--------------------------|---------------------|

|                          | For LXeTPC          |

| <b>Channels</b>          | 8                   |

| <b>Input charge</b>      | -0.025 pC~ 0.025 pC |

| <b>Conversion gain</b>   | 8.2V/pC             |

| <b>Die size</b>          | 3 mm x 3 mm         |

| <b>Peaking time</b>      | 1 us (variable)     |

| <b>Power dissipation</b> | Less than 10mW/ch   |

# プリアンプの調整

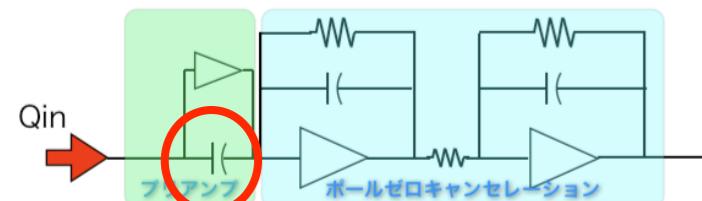

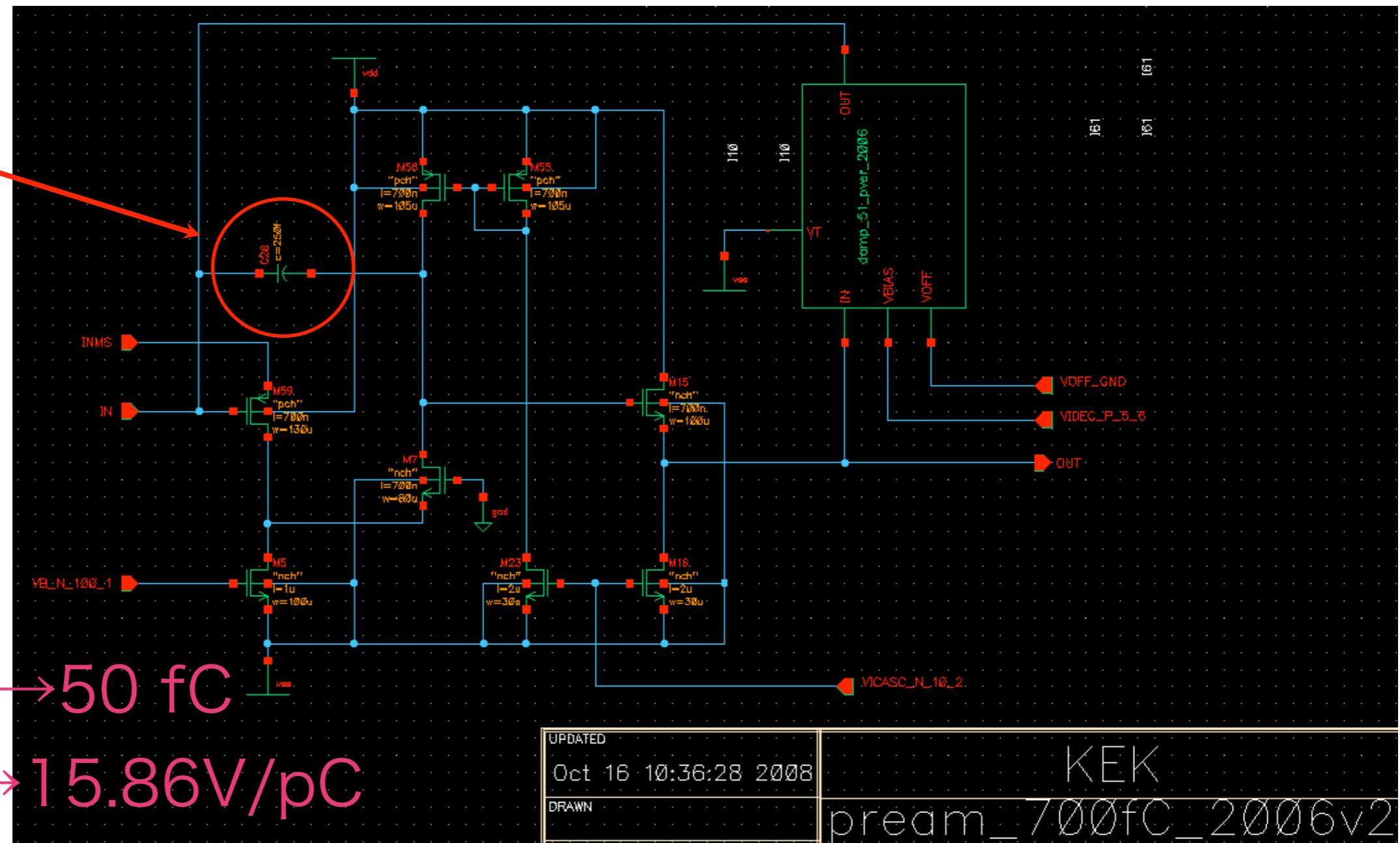

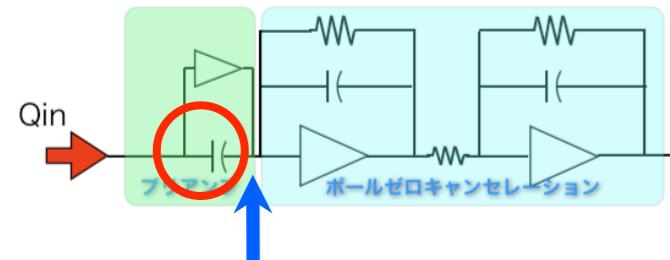

# プリアンプの回路図

キャパシタンスの

容量でゲインが決

まる。

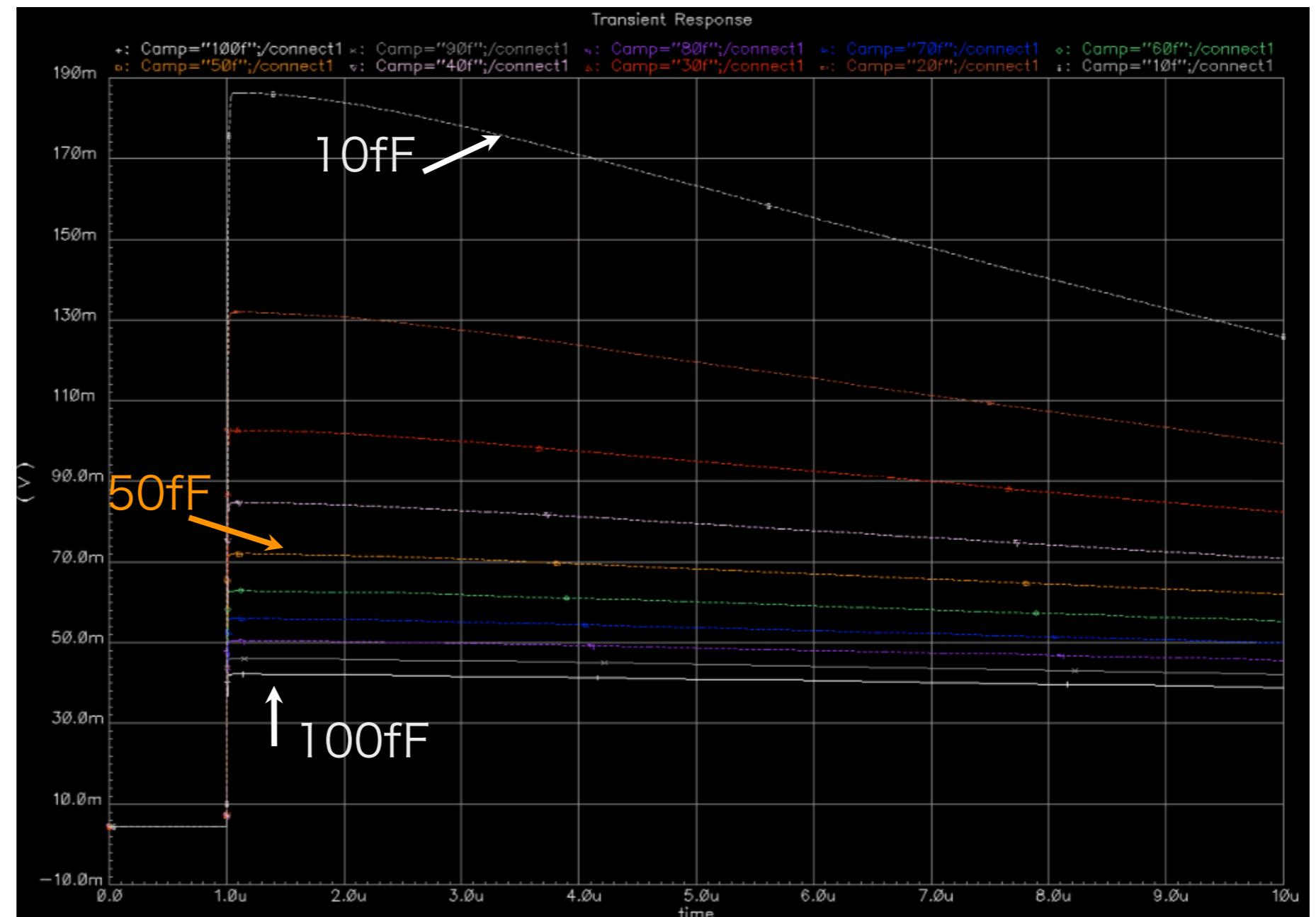

# プリアンプの出力

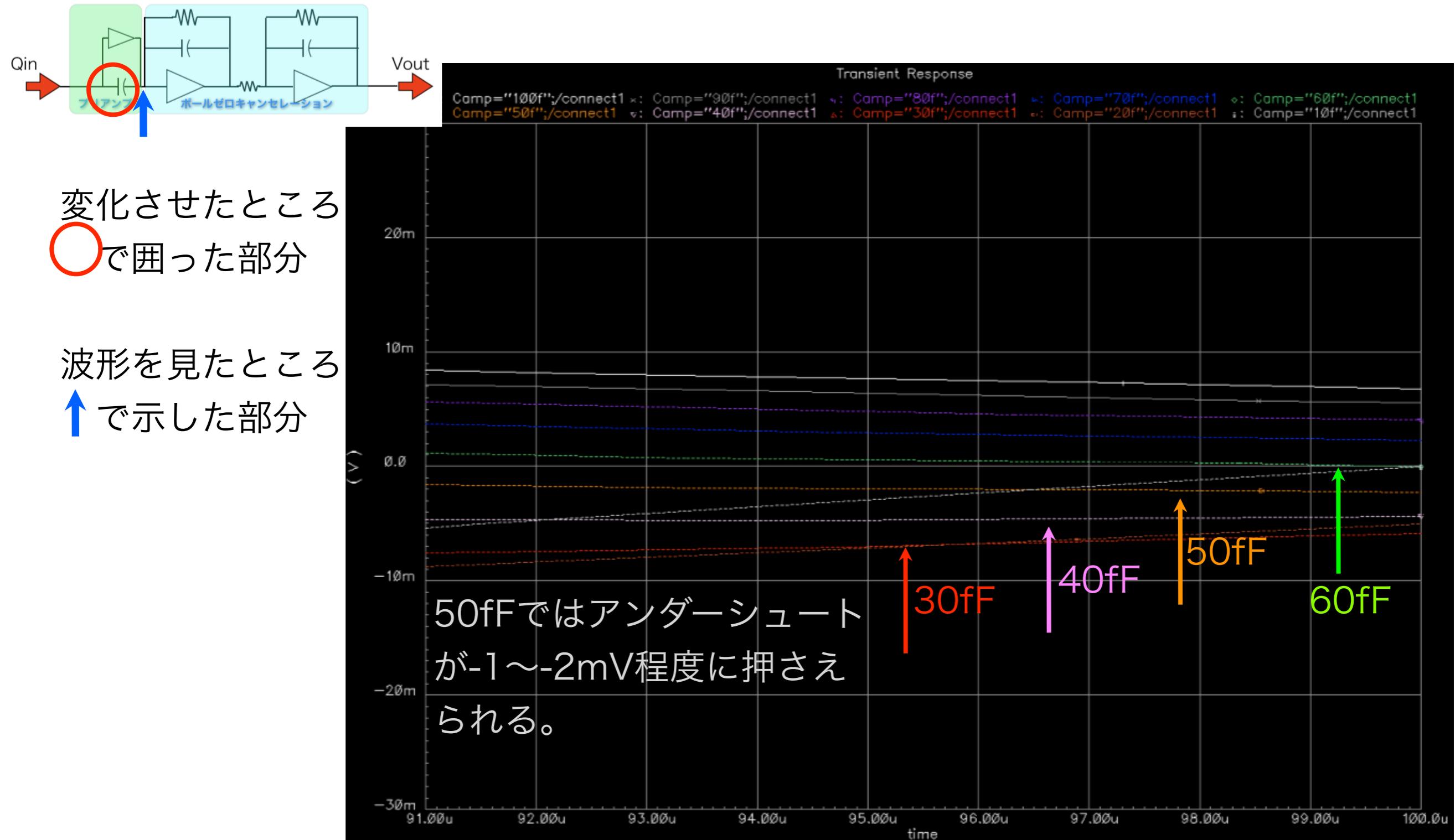

変化させた素子=

○で囲った部分

波形(電圧)を見た部分=

↑で示した部分

5fC入力に対する

プリアンプの出力

キャパシタンスを

10fF~100fFに変化

(10f毎)

## ● ゲインの調整

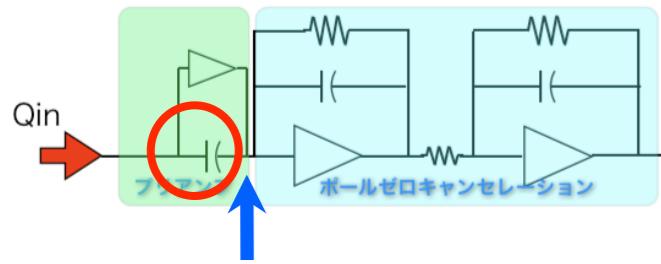

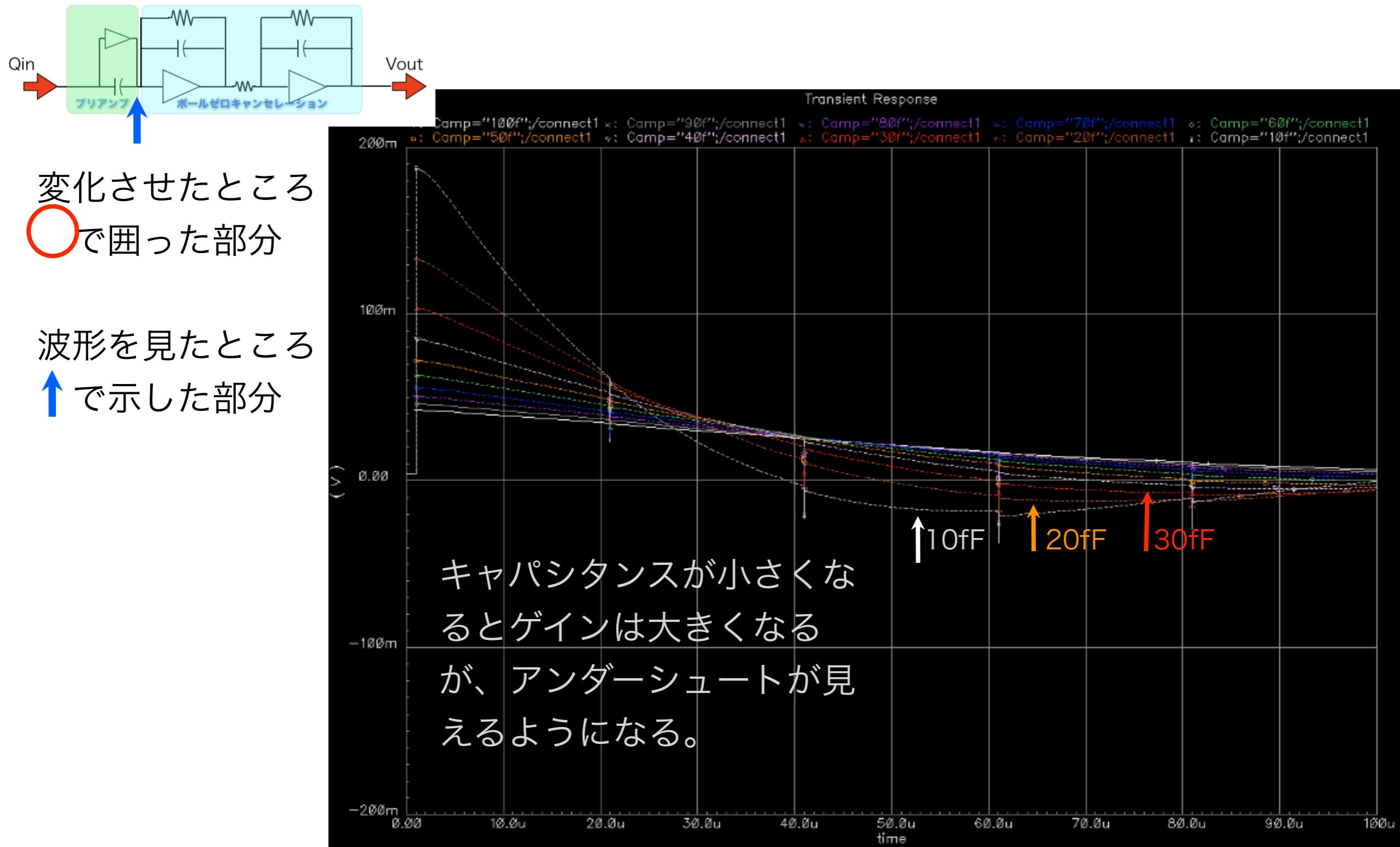

# プリアンプの出力

変化させたところ

○で囲った部分

波形を見たところ

↑で示した部分

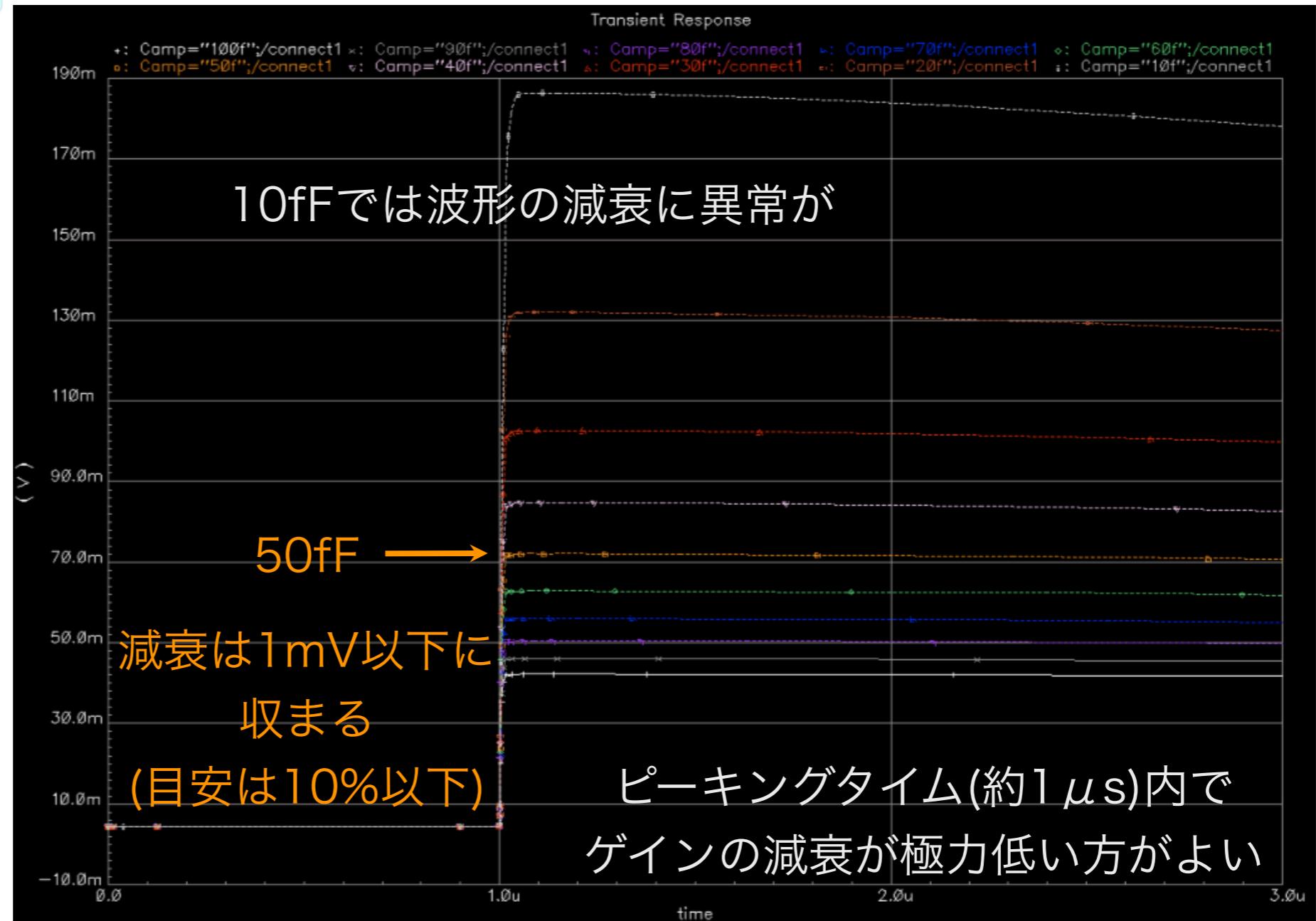

# プリアンプの出力

# プリアンプの出力