液体キセノンTPC用

ASICデザイン

東貴俊

# 仕様

\* 隣りチャネル

|                         | FE2006             | For LXeTPC                     |

|-------------------------|--------------------|--------------------------------|

| 入力電荷範囲                  | -1.5 ~ 1.5pC       | -75 ~ 25fC                     |

| ゲイン                     | 0.44V/pC           | 31.68V/pC                      |

| ゲインばらつき                 | 15%                | なるべく低く(~1%)<br>目標値             |

| コンパレータ入力ゲイン             | 1.3V/pC            | コンパレータ無し                       |

| ノイズ                     | 5900e(Cd=100pF)    | 2000e予定(Cd=1pF)<br>まだ測定できていない。 |

| クロストーク                  | 0.6% (1~3%*)       | なるべく低く(~1%)<br>目標値             |

| ピーキングタイム                | 30ns               | 1us                            |

| V <sub>th</sub> 補償用 DAC | 1 ~ 30mV (1mV/bit) | 無し                             |

| 消費電力                    | 29mW/ch            | ? mW/ch                        |

| 温度耐性                    | 未測定                | -100°C                         |

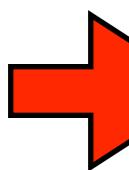

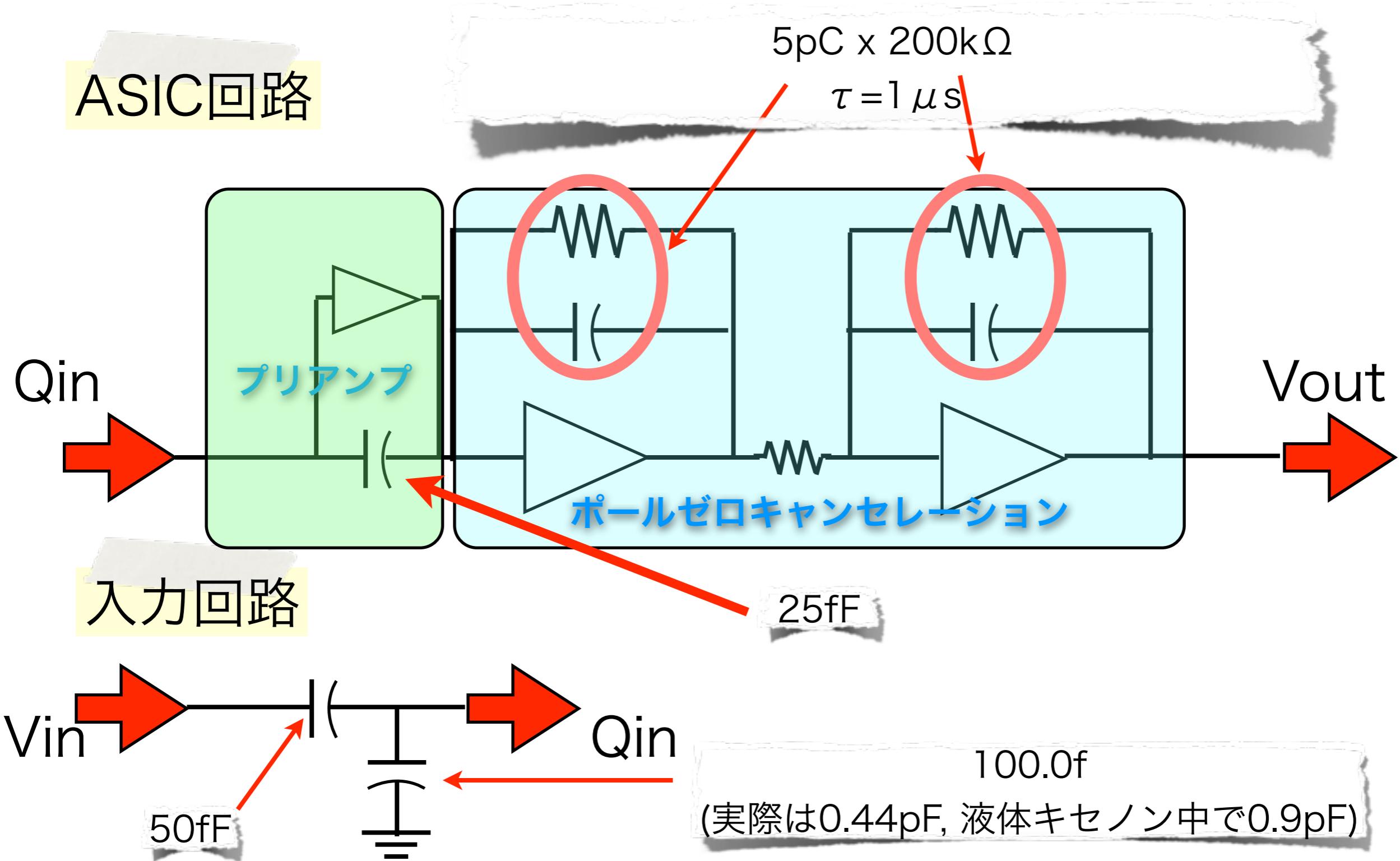

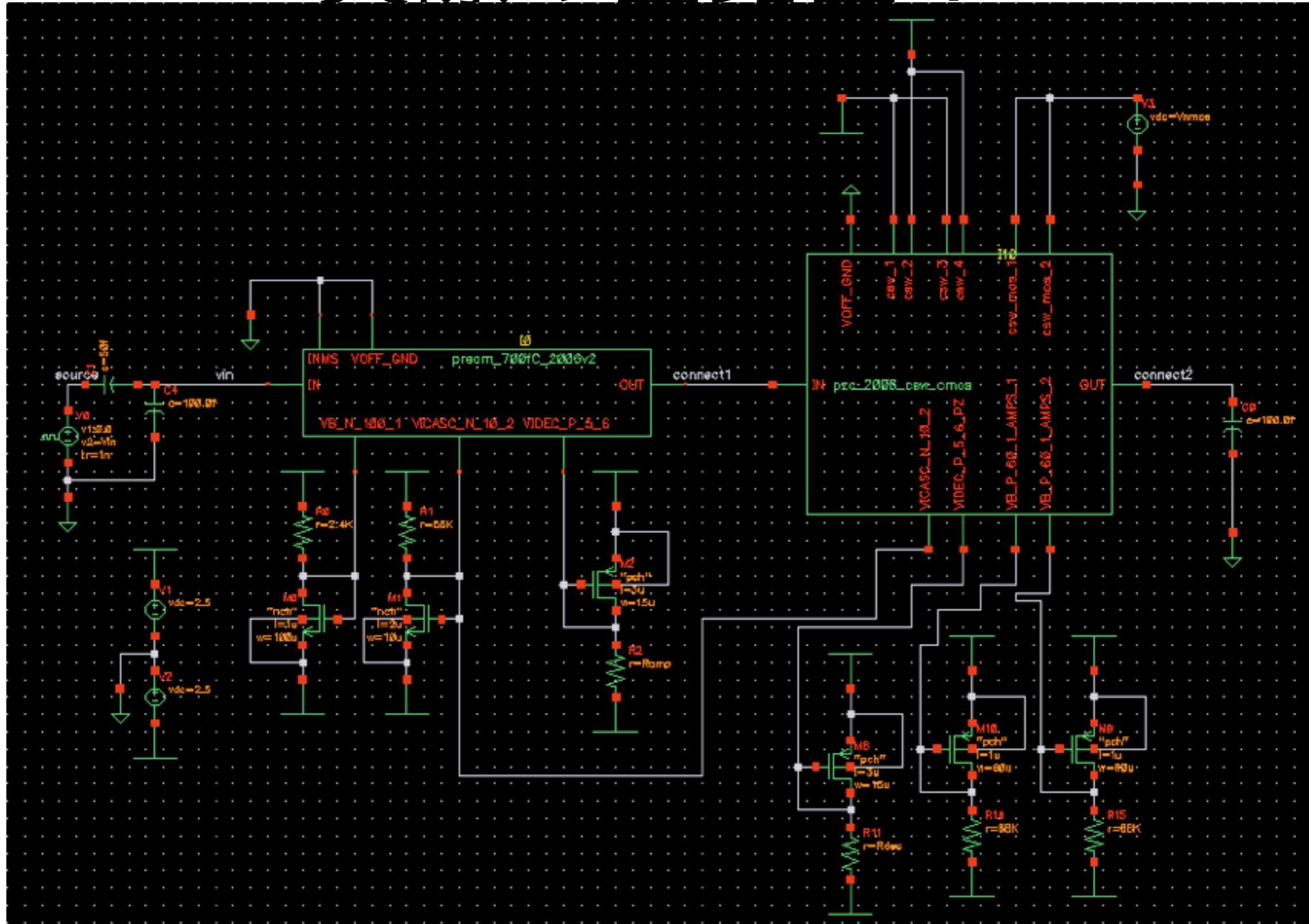

# テスト回路の簡略図

## ASIC回路

$Q_{in}$

プリアンプ

この素子の値を決めるこことにより時定数  $\tau$  が決まる。

$$\tau = CR$$

$V_{out}$

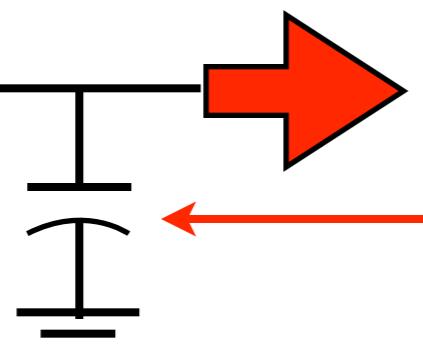

## 入力回路

$V_{in}$

検出器容量

入力電荷を貯める

キャパシタンスの大きさにより

ゲインが変化する。

# テスト回路の簡略図

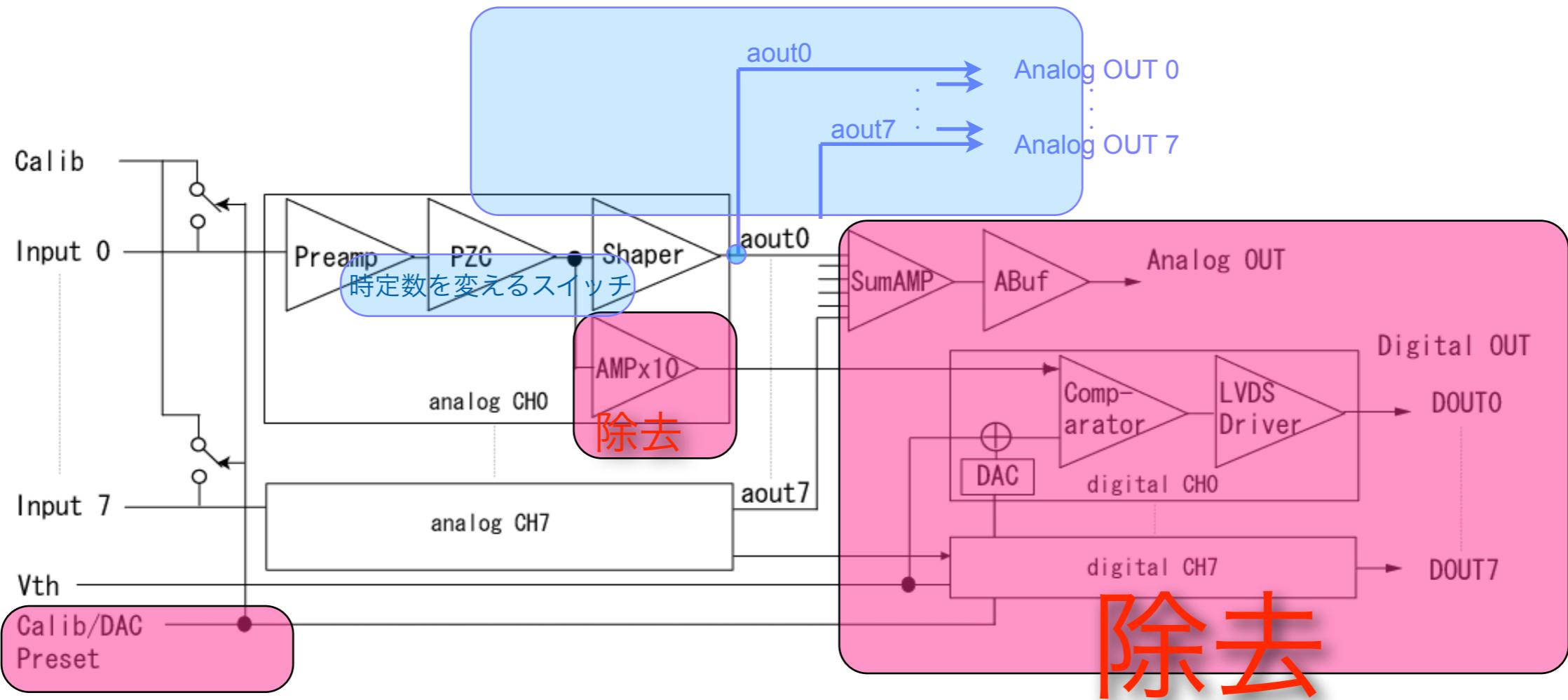

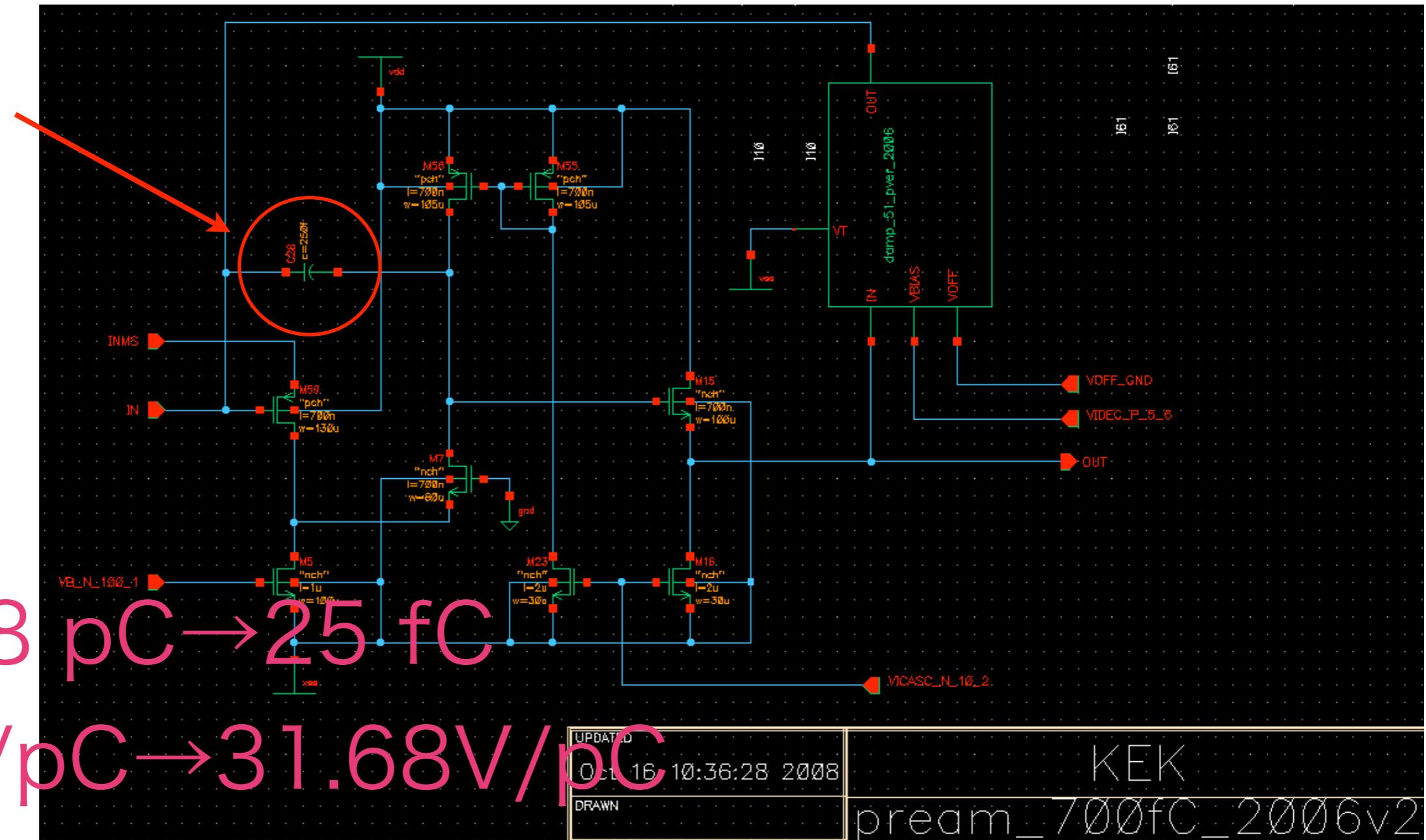

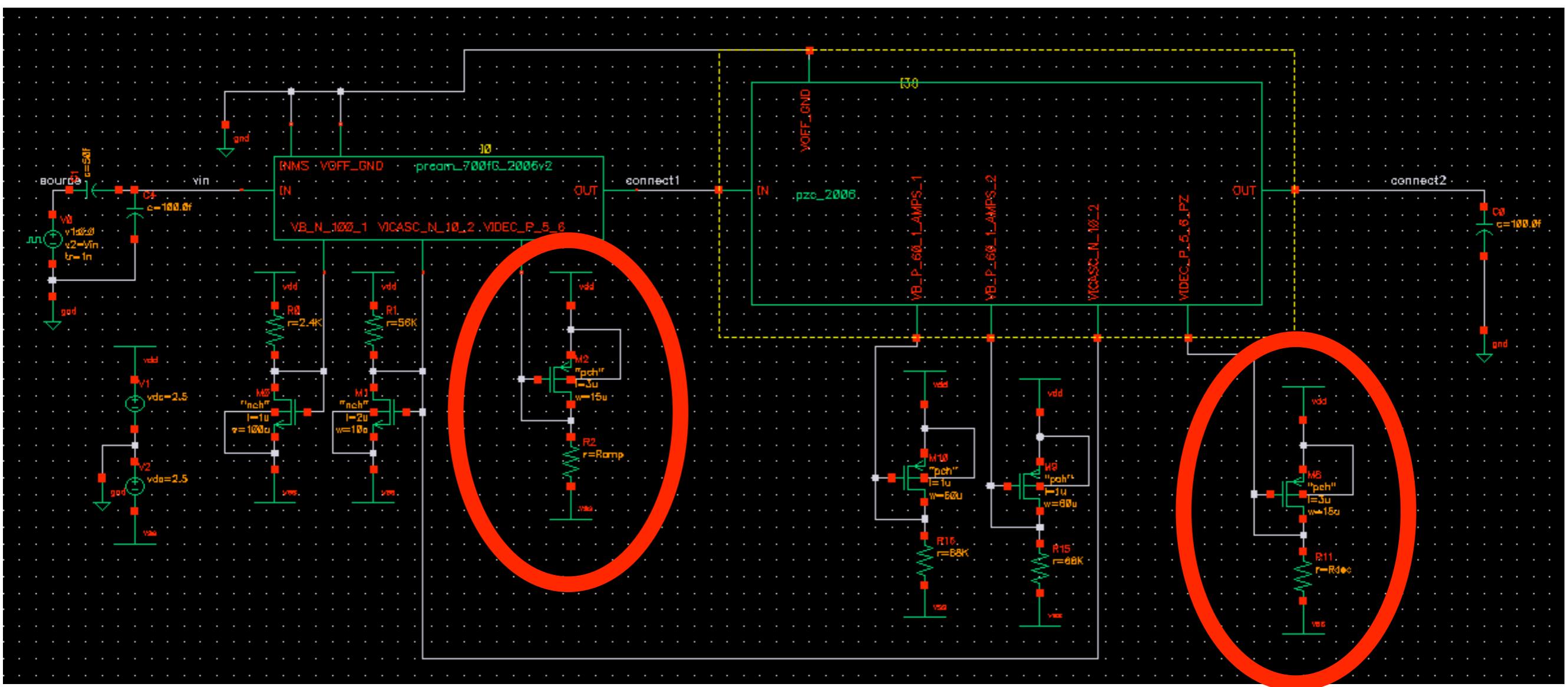

# FE2006回路を変更

赤：無くす部分

青：加える部分

シミュレーション

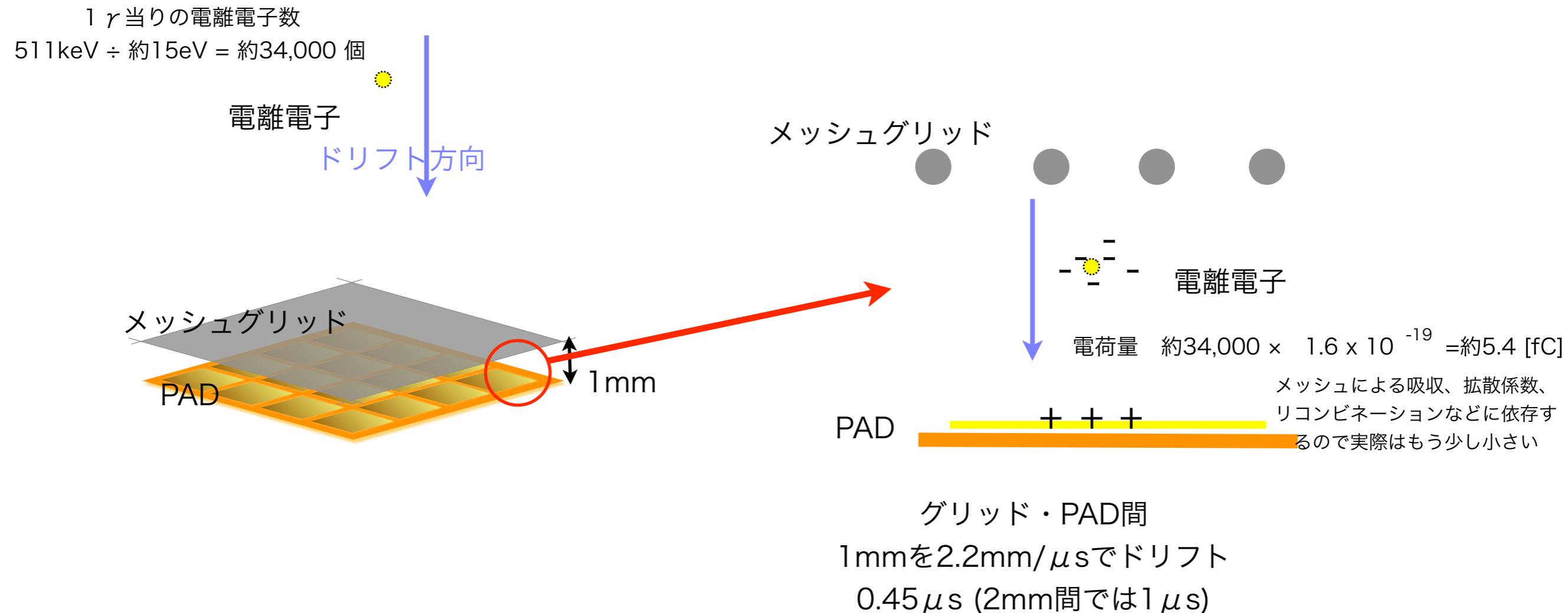

# 入力信号

1  $\gamma$  による信号の入力電荷を

1~5[fC]程度で設定

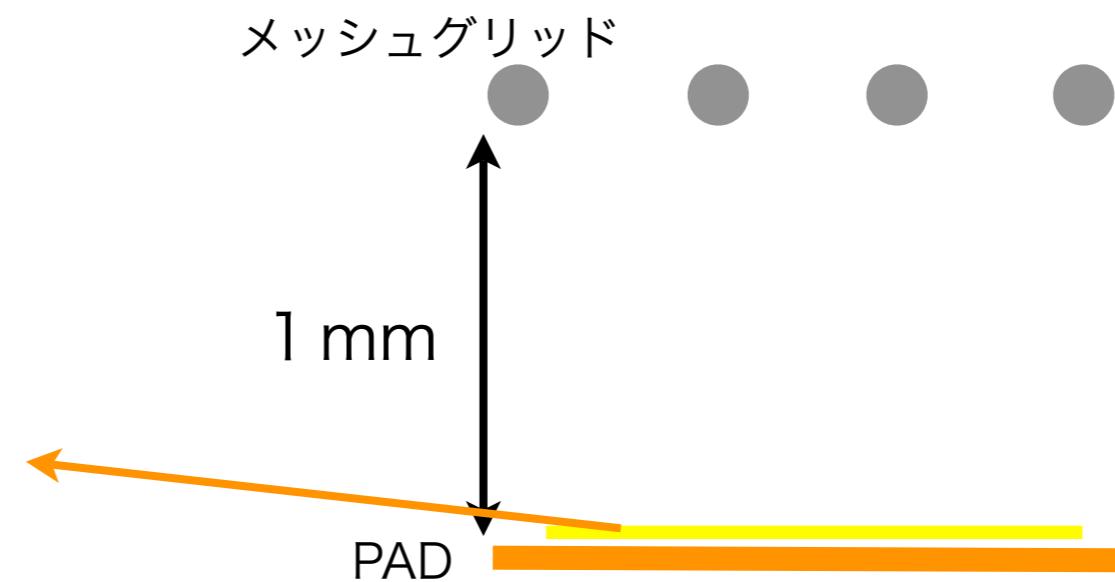

# 静電容量

gridとPADの距離は2mmで、PADの大きさを1cm x 1cmとすると、この静電容量は約0.44pFとなる。

(液体キセノン中では約0.9pFとなる。)

グリッド・PAD間

1mmを2.2mm/μsでドリフト

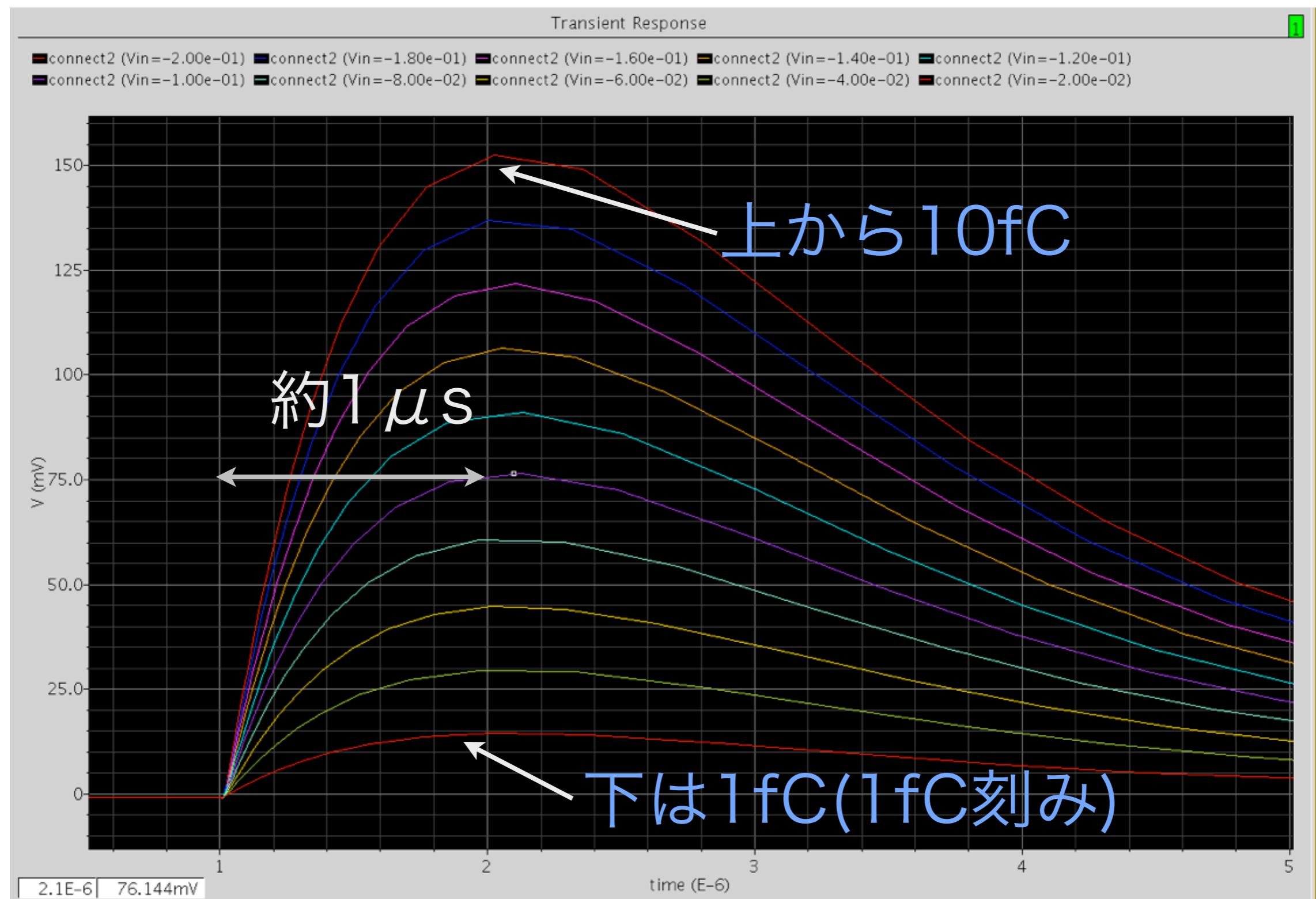

0.45μs (2mm間では1μs)

# ゲインの調整

## プリアンプの回路図

キャパシターの

容量でゲインが

決まる。

1.8 pC → 25 fC

0.44V/pC → 31.68V/pC

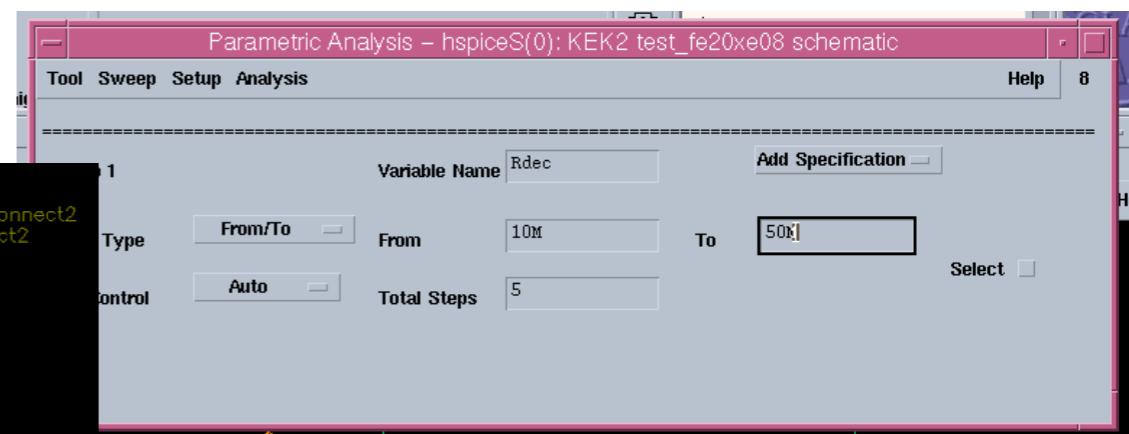

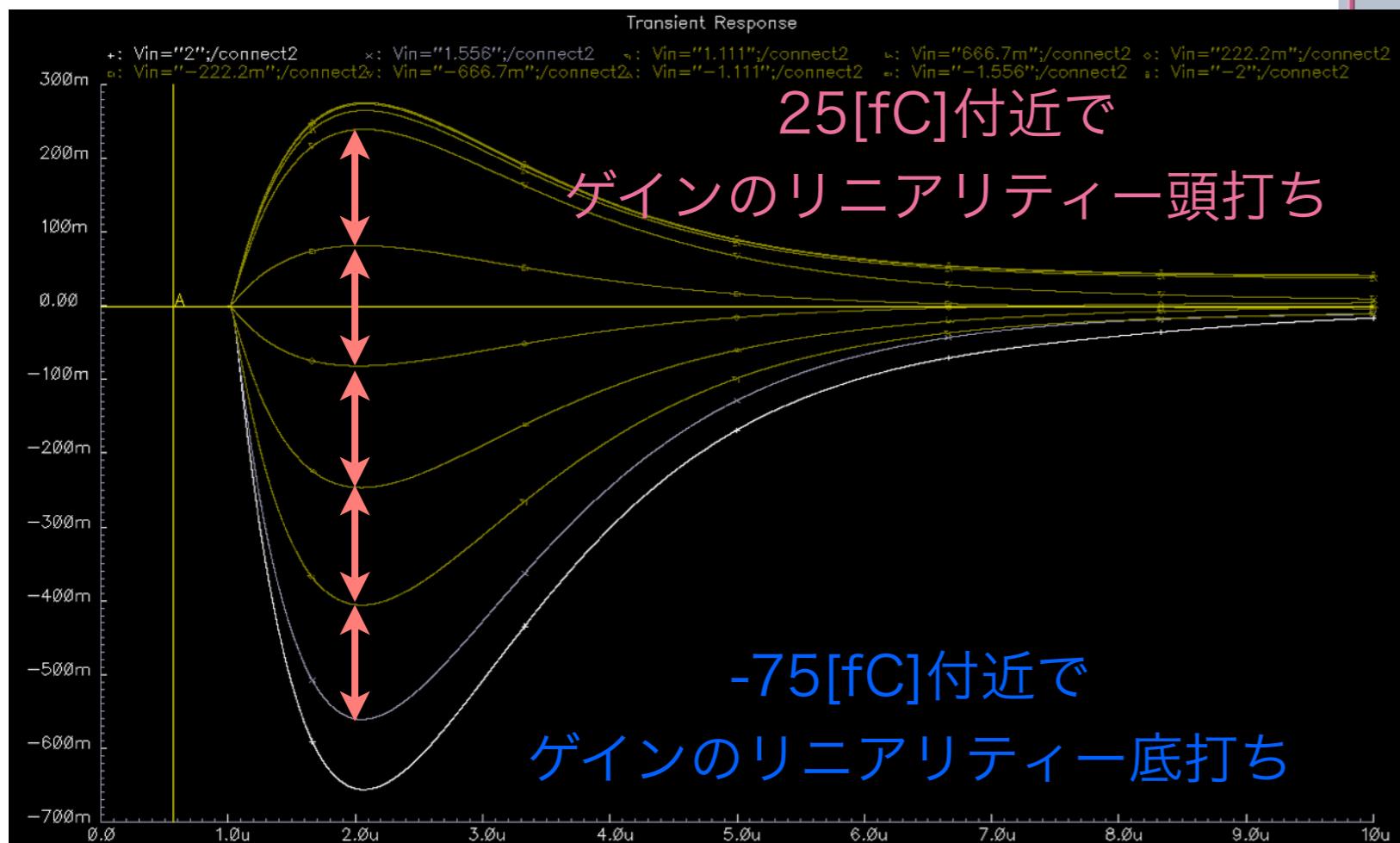

# 入力電荷範囲の確認

- 入力電荷を100[fC] ~ -100[fC]まで10ステップを確認

パラメトリックプロットを使用

抵抗値、キャパシター、電源など

あらゆるパラメータを変化させて

プロットできる。

時間があれば

原因を考察したい。

# バイアス電流の調整

抵抗値を変えることで中の抵抗器の電流が変化

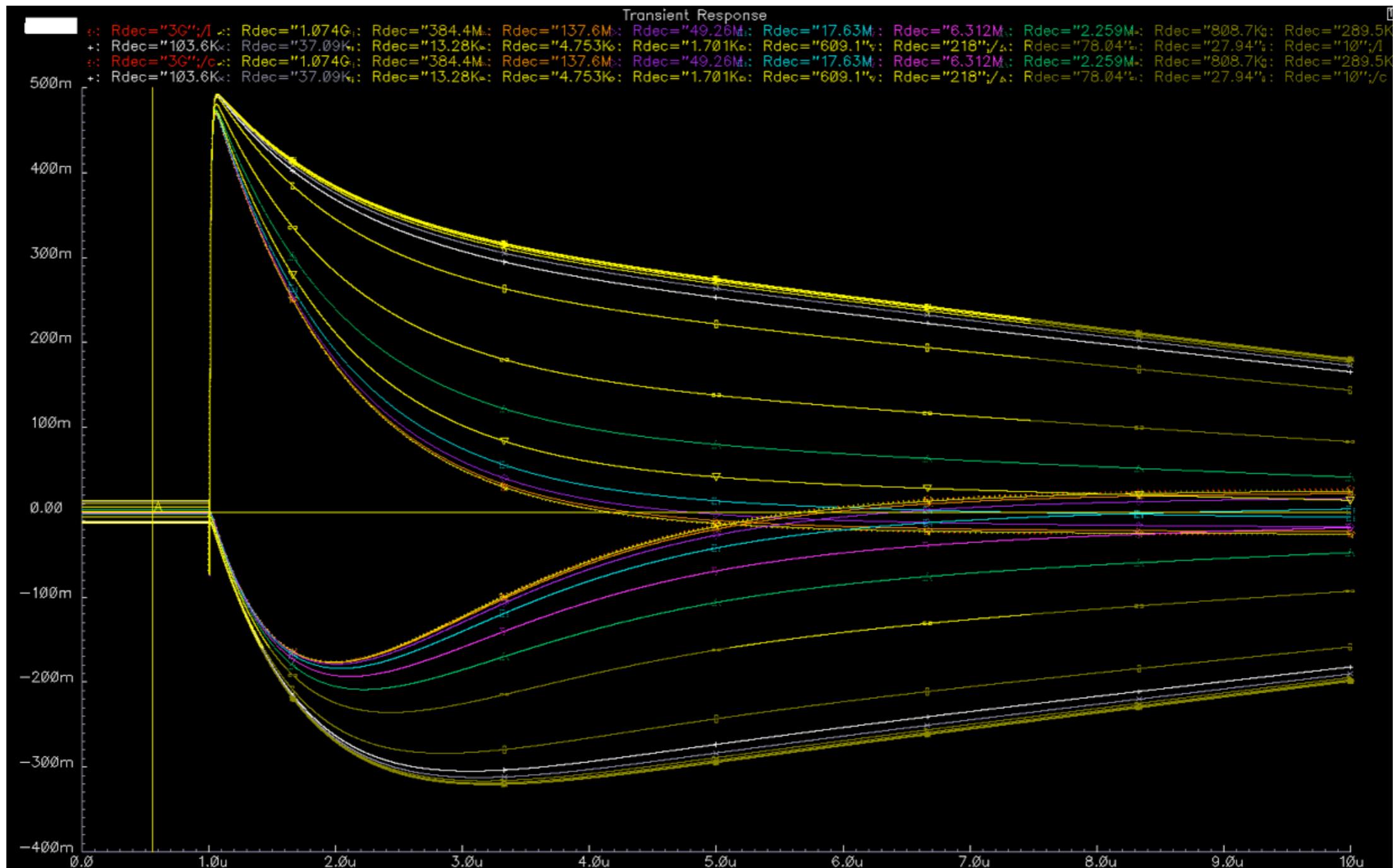

# パラメトリックプロット

さまざまな抵抗値を与えて

アンダーシュートがなくなる抵抗値を探った。

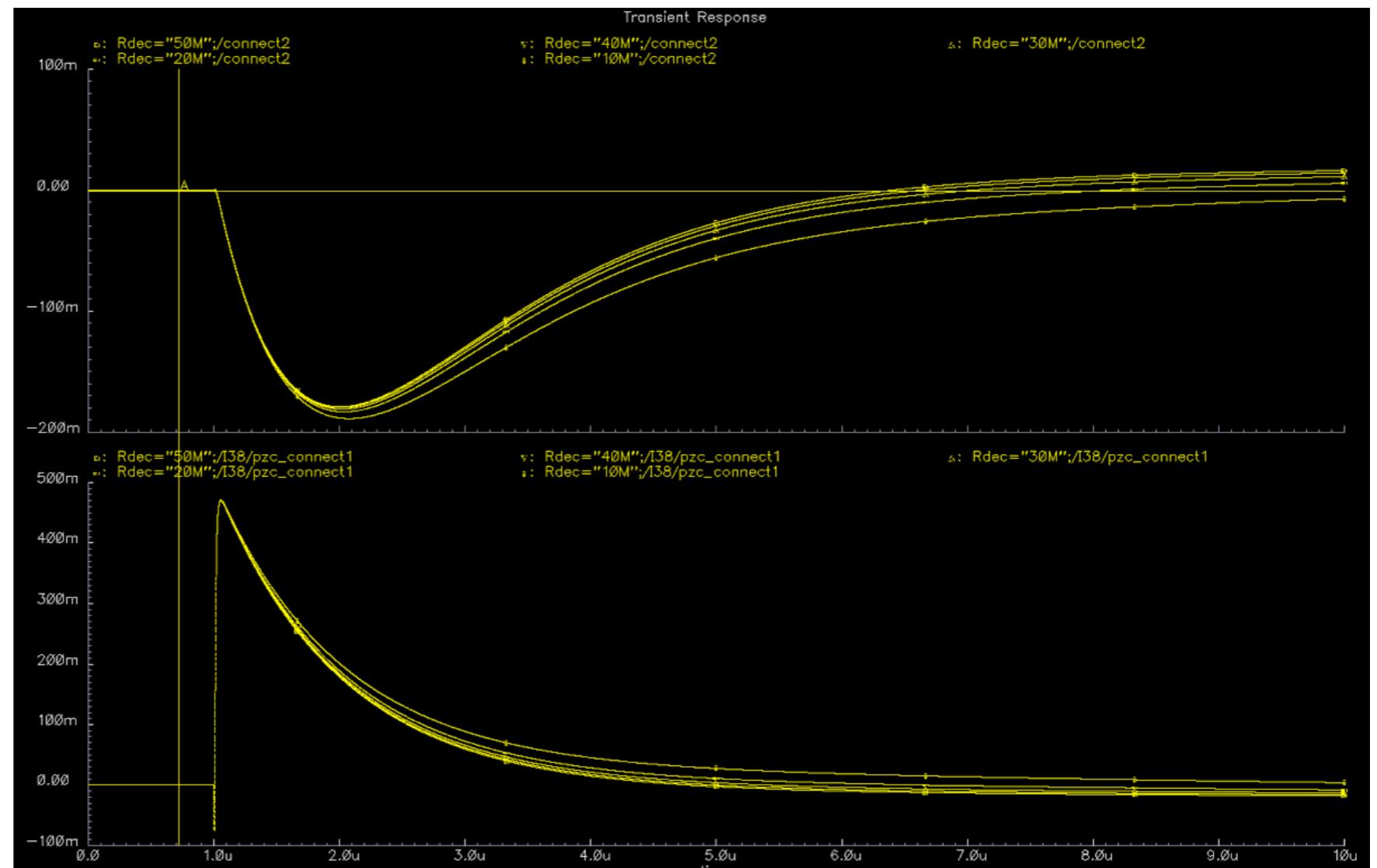

# 抵抗値の決定

15M ~ 20M  $\Omega$ の間がよさそうなので

17.5M $\Omega$ に設定した。

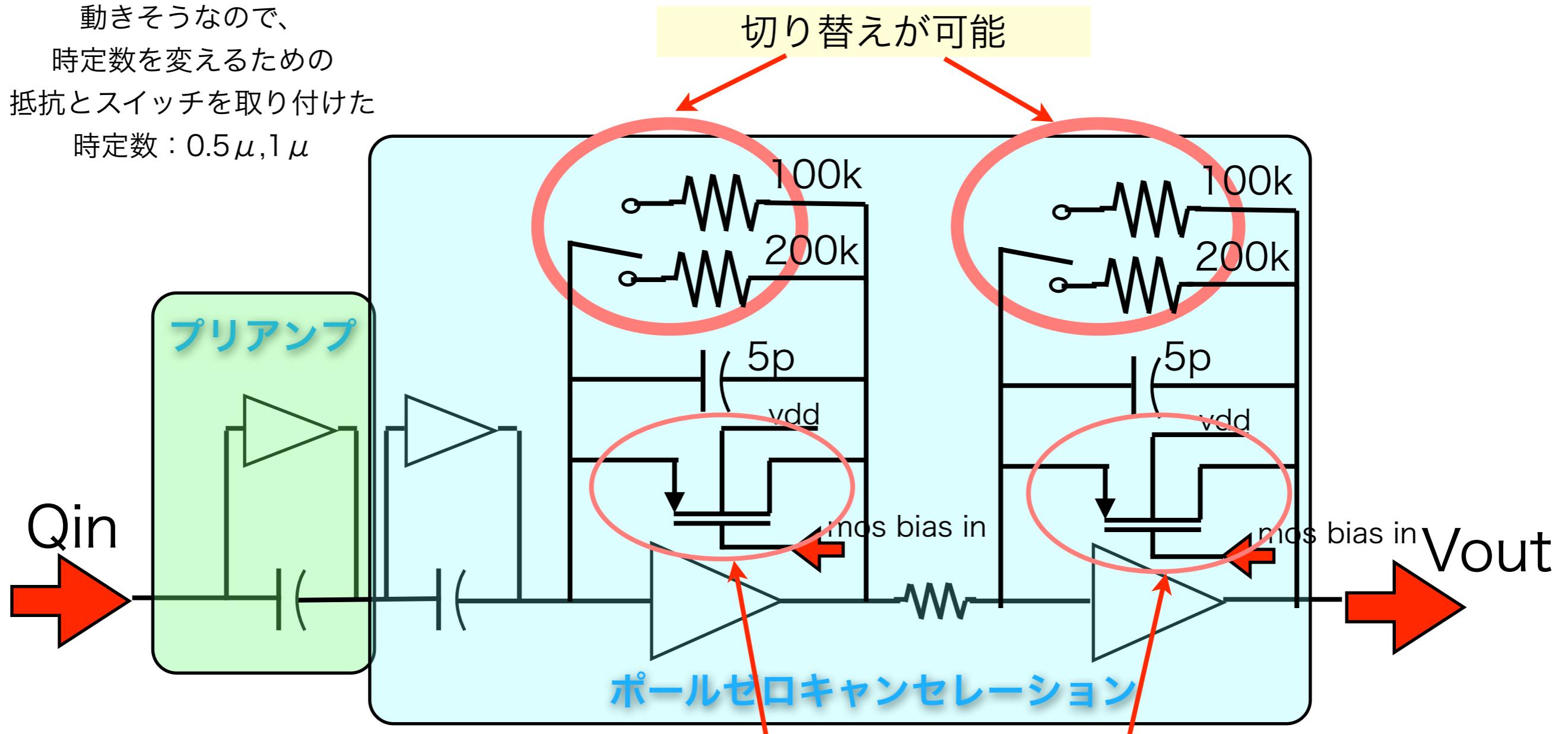

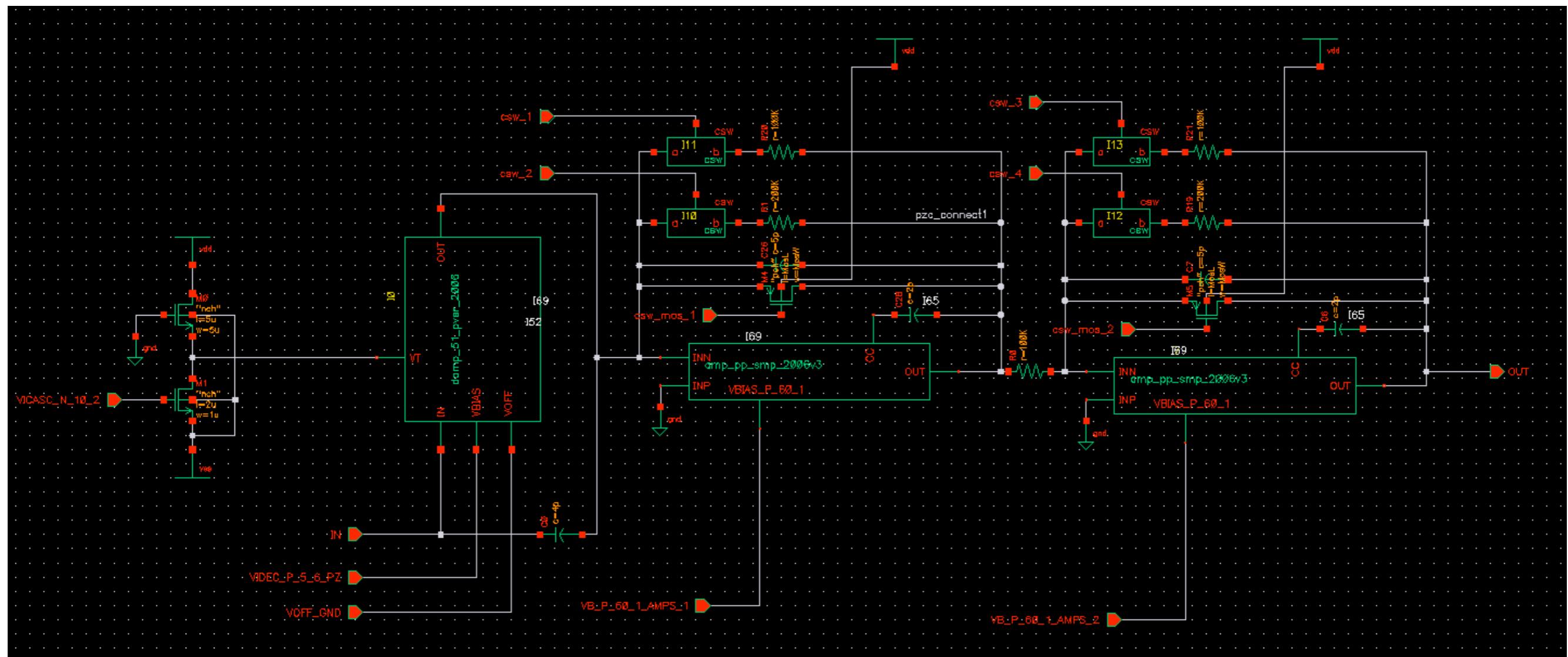

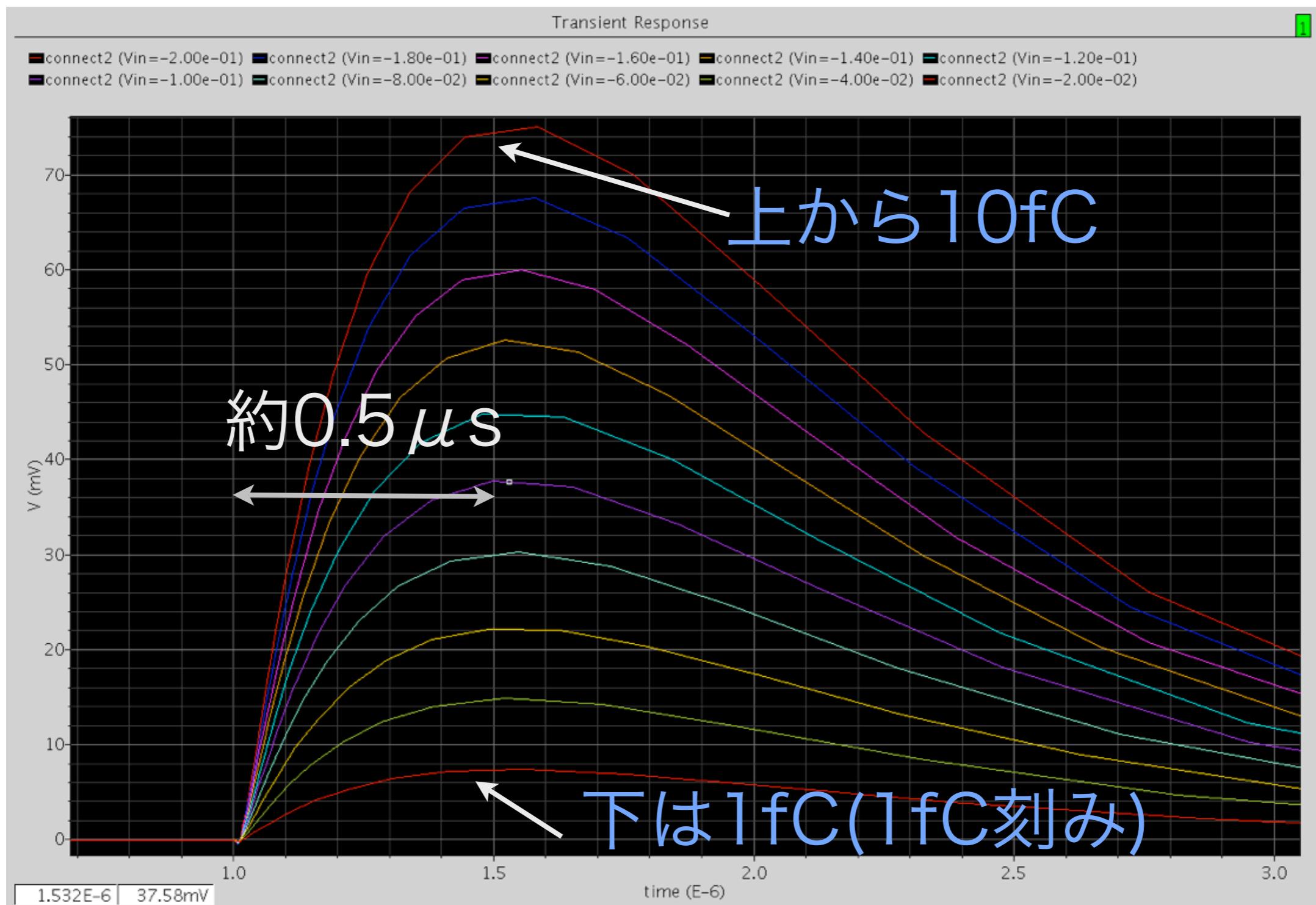

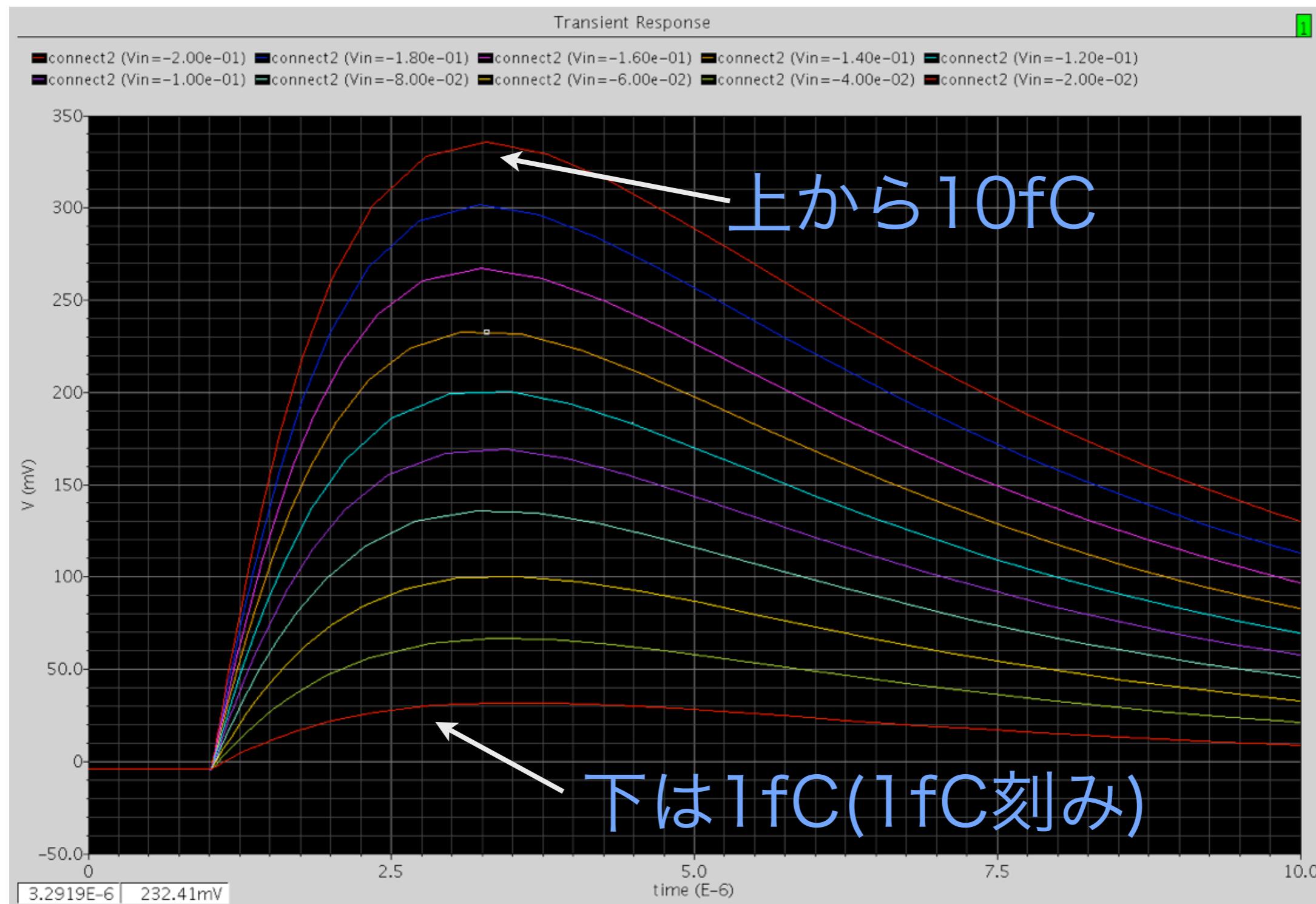

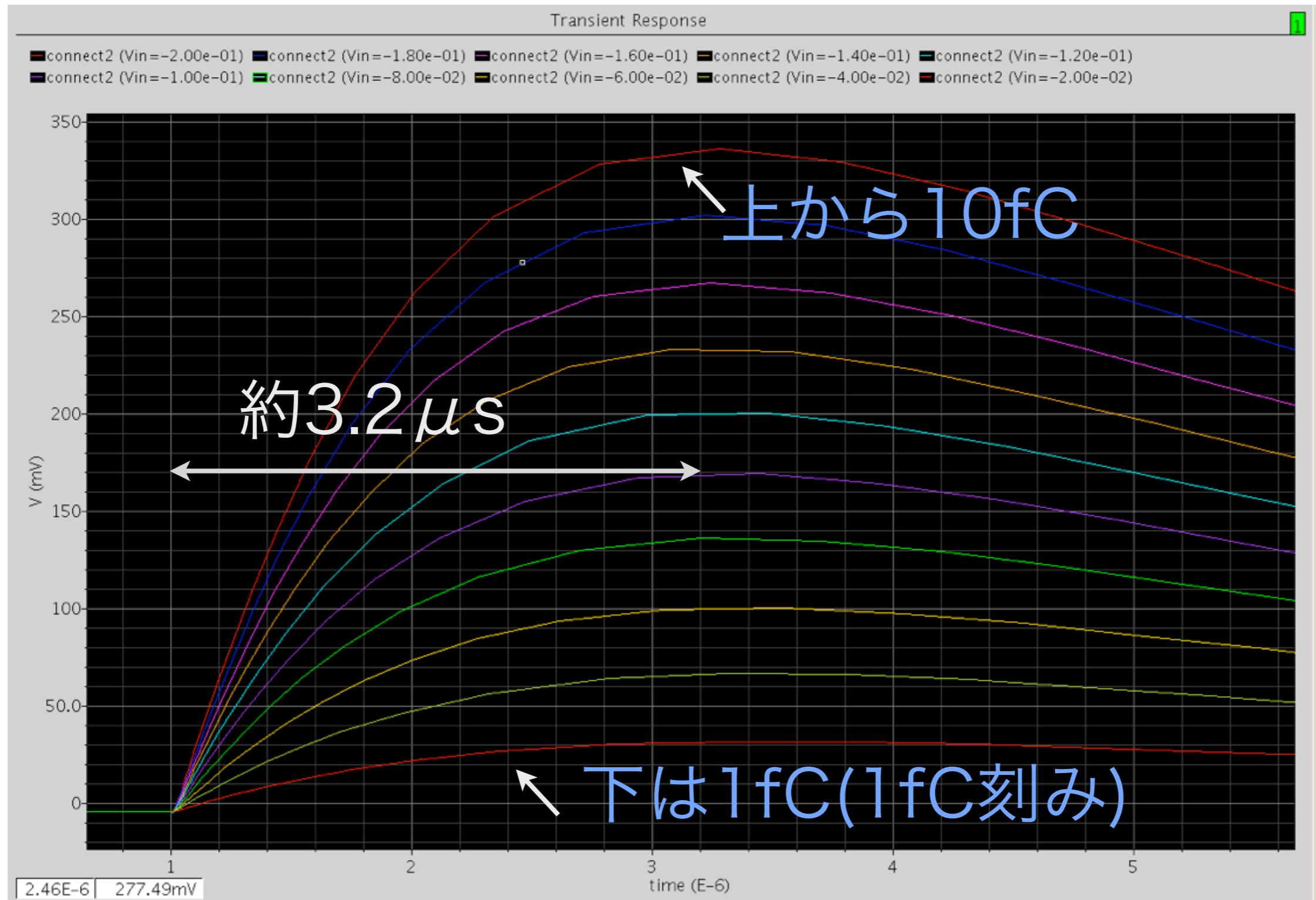

# 時定数の切り替え

# テスト回路の簡略図

動きそうなので、

時定数を変えるための

抵抗とスイッチを取り付けた

時定数 :  $0.5\mu, 1\mu$

pMOSに外部から

バイアス電圧をかけることにより

時定数を連続的に変化させることが可能

時定数を連続的に

変化させることが可能

# 実際の回路図 1

# 実際の回路図 2

## (pole zero cancellation)

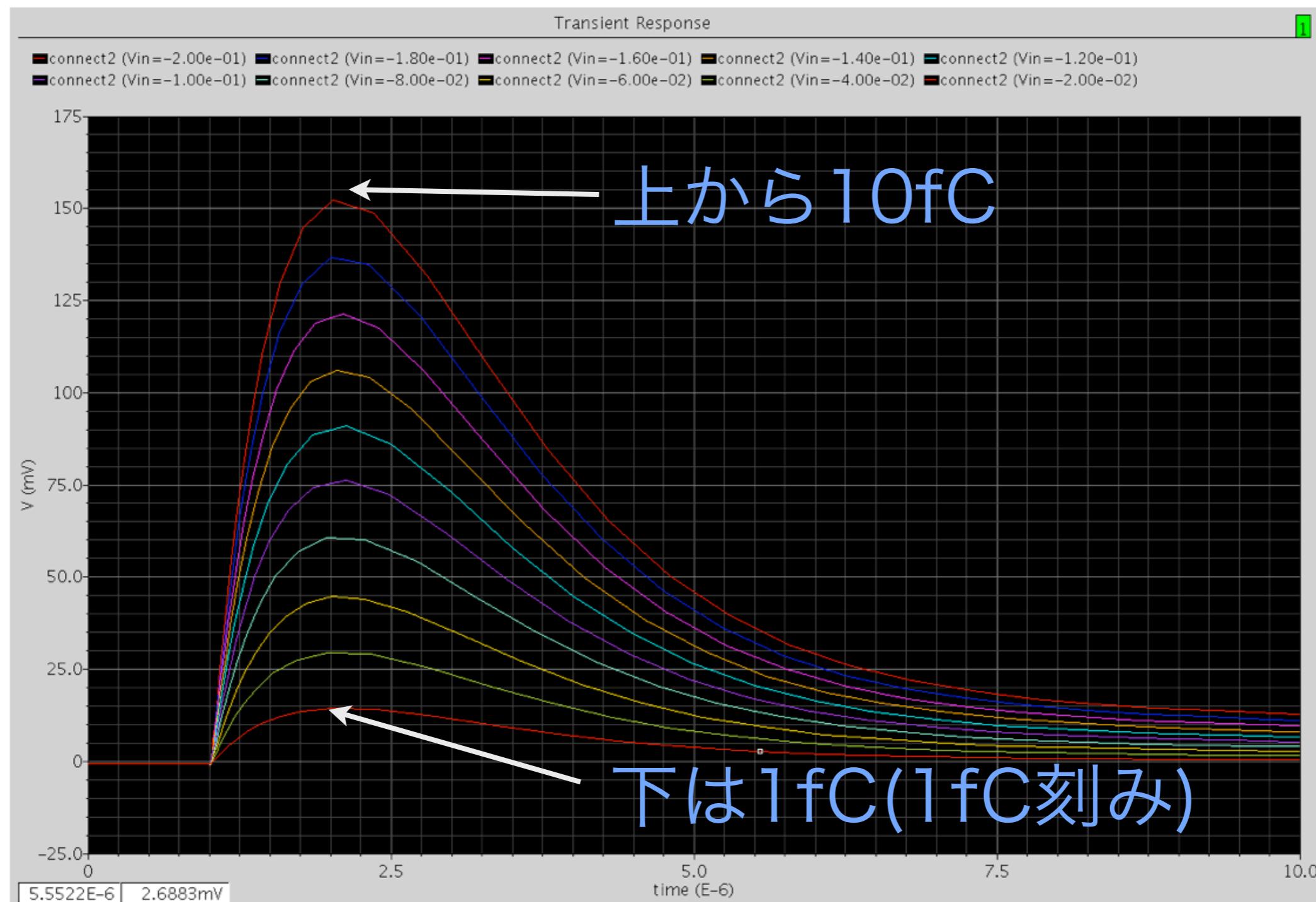

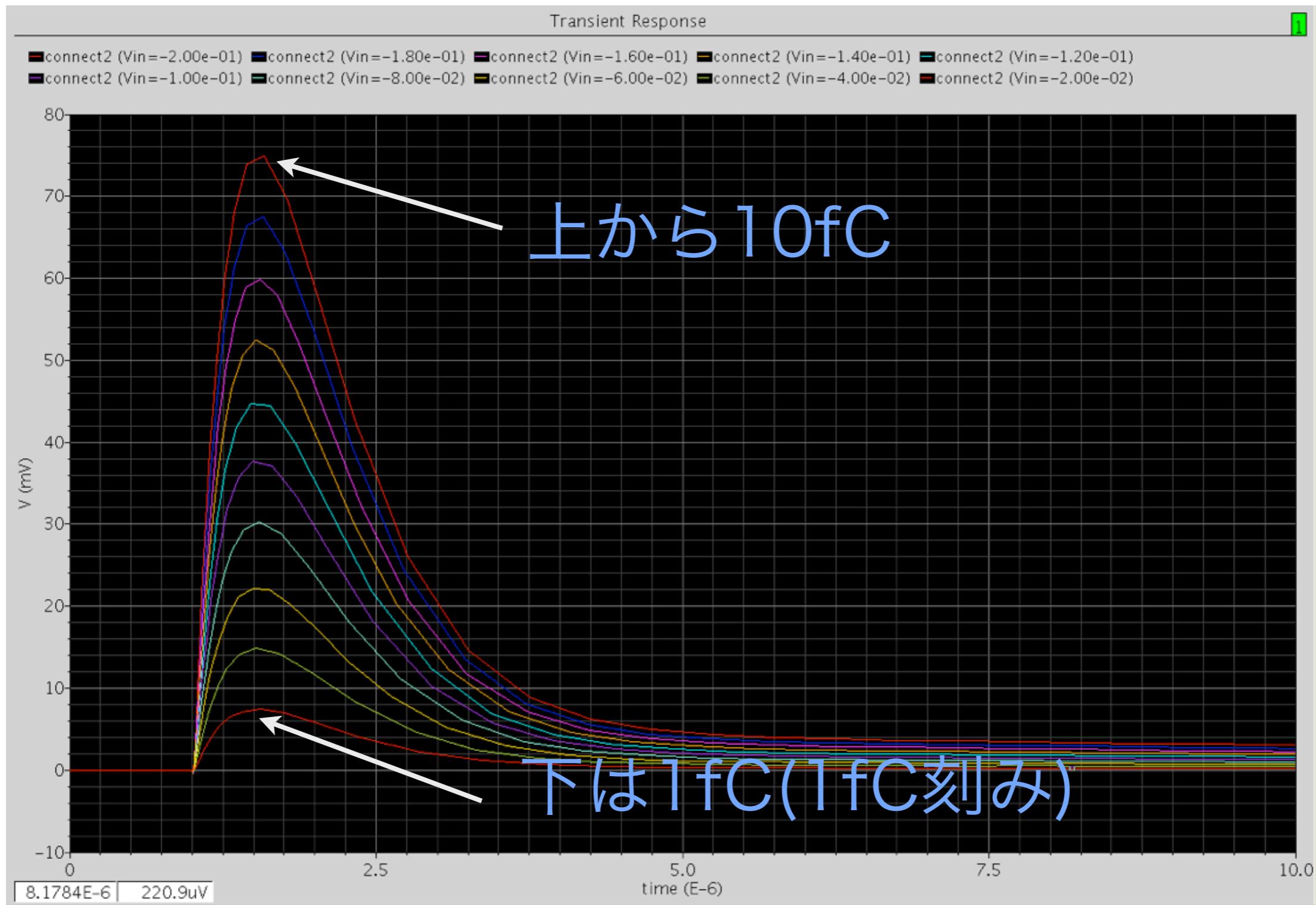

# 確認

回路が正常に動くかを確認する

まず、電荷を1f~10f[C]を

与えたときの出力をみた

# スイッチ(200Ω)

# スイッチ(200Ω)

# スイッチ(100Ω)

# スイッチ(100Ω)

# pMOS(@-1.55V)

# pMOS(@-1.55V)

# スイッチ仕様に先立ちって

- ## 抵抗の決定

今回、時定数を  $1 \mu\text{s}$  に設定している。そのために使用した抵抗およびキャパシターはそれぞれ  $200\text{k}\Omega, 5\text{pF}$  であり、それぞれに大きさを要する。

しかし  $10\text{pF}$  と  $200\text{k}\Omega$  を比べた場合に、両方とも大きいが  $200\text{k}\Omega$  の方がまだマシであるので今回の決定に至った。

スイッチで切り替えるための抵抗、

キャパシター両方をつける考えもあったが、

やはり先述のように大きさがあるので抵抗  $100\Omega$  のみとし、

大きな時定数は pMOS で補うこととした。

# スイッチ仕様に先立ちって

- pMOS

pMOS与えるバイアス電圧ならびに

pMOSの大きさに関してパラメト

リックプロットを行ってみた。

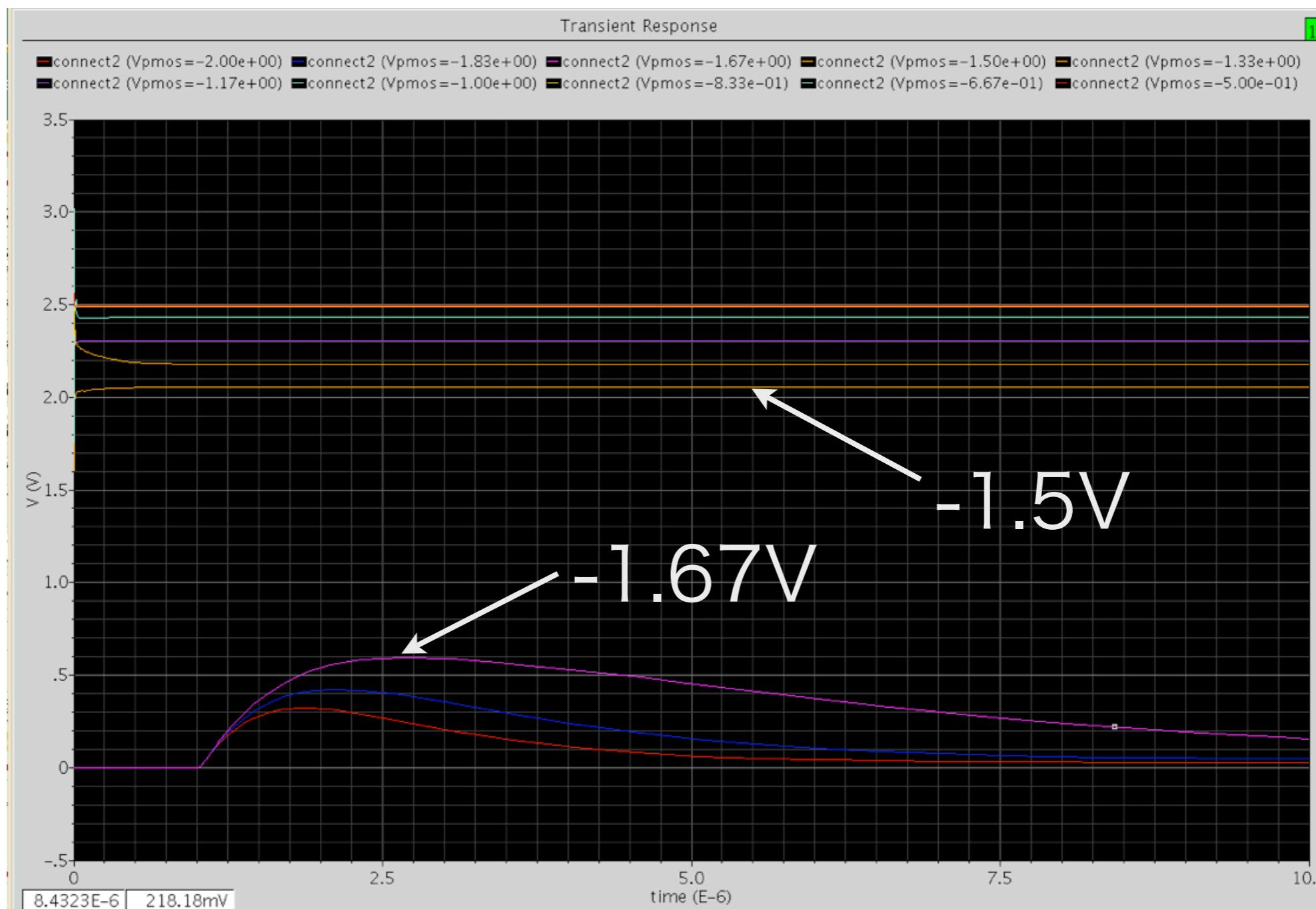

# pMOSのバイアス電圧に対しての出力

- pMOSに与える電圧の変化による出力の変化をみる(-0.5~2.0V)

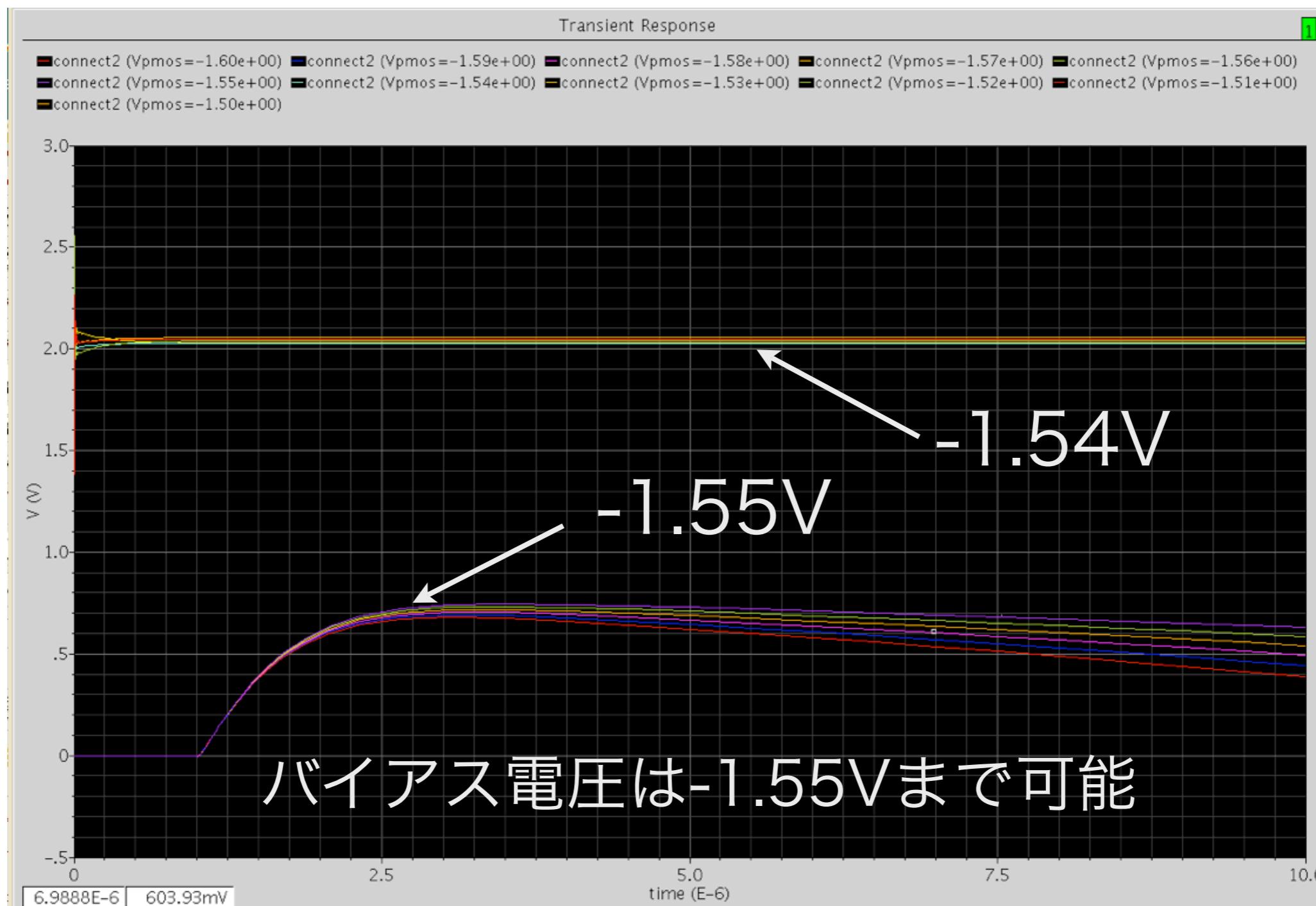

# pMOSのバイアス電圧に対しての出力

- さらに細かくみる(-1.50~1.60V)

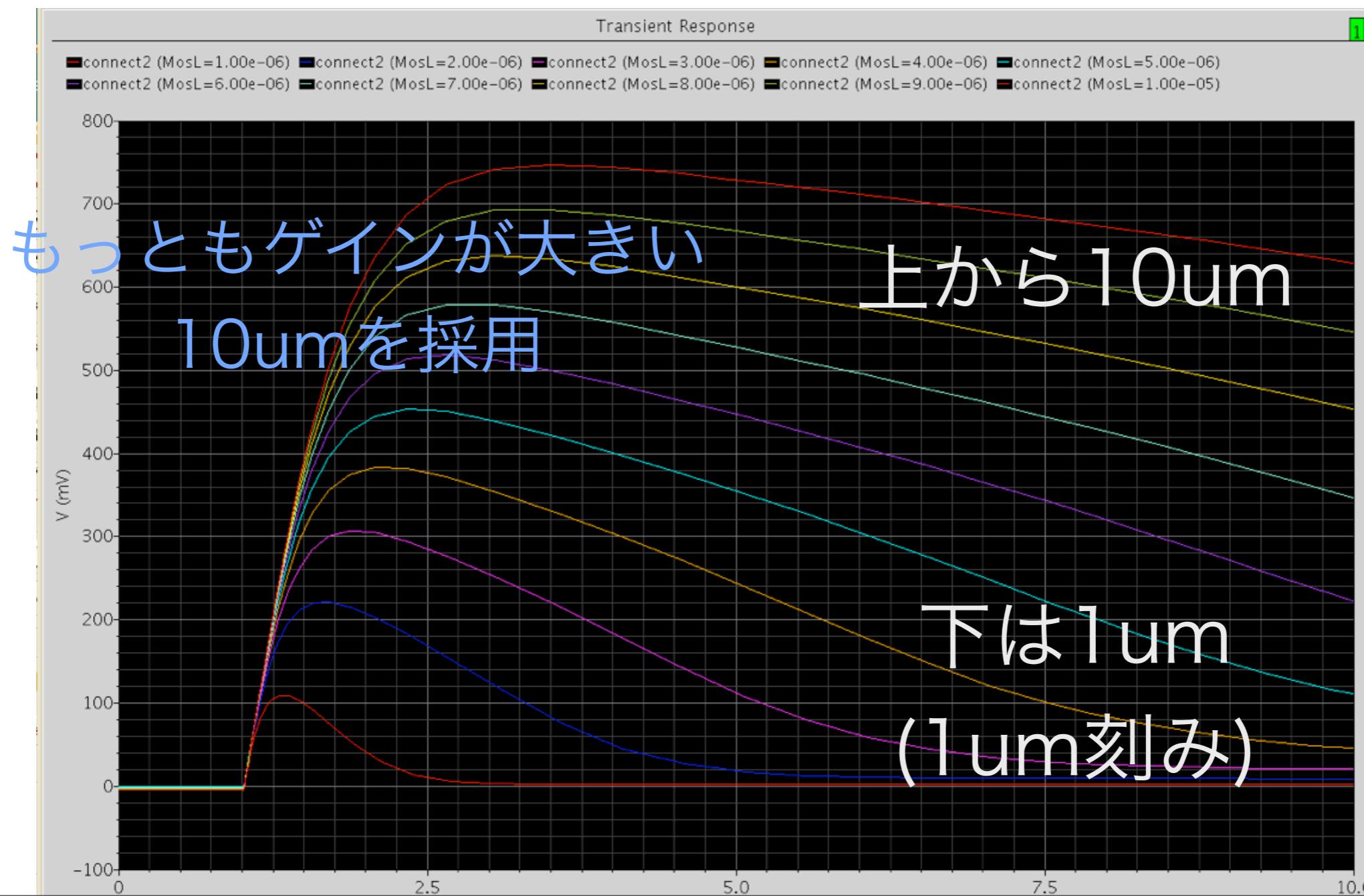

# pMOSの大きさ

- pMOSの大きさ(Length)をパラメトリックプロットでシミュレーション

# 予定

- ・コーナーシミュレーションを行い、今回見たような入力電荷に対しての出力がどのようにあるかを調べたい

- ・来週にはレイアウトデザインに入りたい

資料

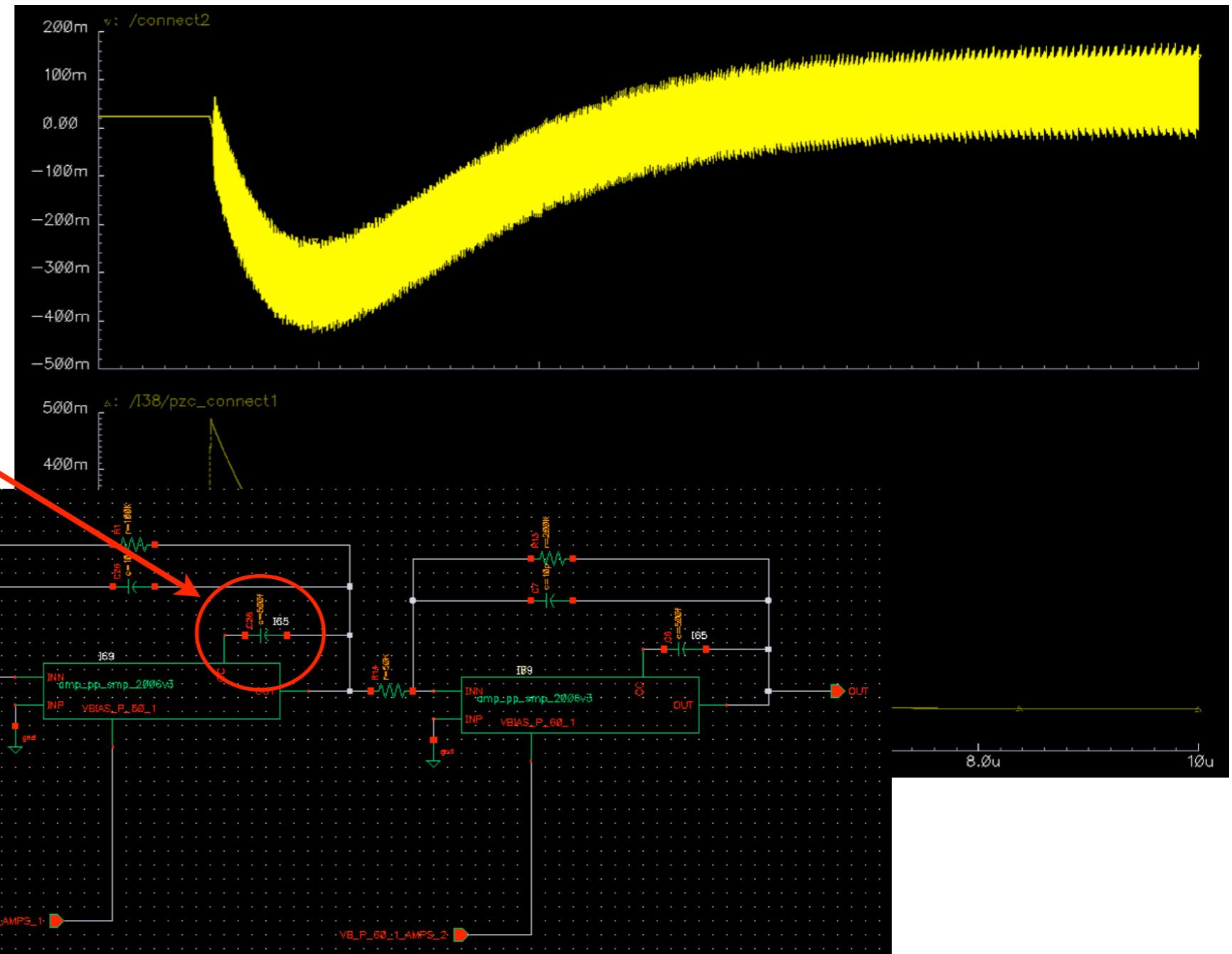

# トラブルシューティング

右のような波形が見えたが

これはシミュレーションに

によるトラブル

容量値を変えることで

消えた。