# Progress in the development of the vertex detector with fine pixel CCD at the ILC

Constantino Calancha Paredes\*1, A. Dubey2, H. Ikeda3, A. Ishikawa2, S. Ito2, E. Kato2, A. Miyamoto1, T. Mori2, H. Sato4, T. Suehara2, Y. Sugimoto1, H. Yamamoto2

High Energy Accelerator Research Organization<sup>1</sup> Tohoku University, Department of Physics<sup>2</sup> Institute of Space and Astronautical Science, JAXA<sup>3</sup> Shinshu University<sup>4</sup>

E-mail: calancha@post.kek.jp

We are developing the vertex detector with a fine pixel CCD (FPCCD) for the international linear collider (ILC), whose pixel size is 5 x 5  $\mu$ m<sup>2</sup>. ILC physics programme impose several design requirements, as high granularity and low occupancy. FPCCD also impose several requirements in the readout ASIC, mainly, fast readout speed, low noise and low power consumption as well. We present the status of the R&D to achieve those design requirements.

22nd International Workshop on Vertex Detectors September 15th-20th, 2013 Lake Starnberg, Germany

\*Speaker.

# 1. Introduction

The verification of the Higgs mechanism is one of the most important goals within the ILC physics programme. This mechanism is reflected in the Higgs boson couplings.

The measurement of these various couplings requires accurate particle identification; in particular, excellent separation between b-quarks and c-quarks, and between light quarks and gluon are crucial. In order to realize ILC's highly efficient flavor tagging, we need a vertex detector with an impact parameter resolution of  $5 \oplus 10/(p\beta sin^{3/2}(\theta))$  ( $\mu$ m) and a low level of pixel occupancy for accurate track reconstruction. Currently three sensor technology options are actively developed for the ILD <sup>1</sup> vertex detector. Those technological options are CMOS Pixel Sensors (CPS), Depleted Field Effect Transistor (DEPFET) sensors and FPCCD sensors.

Here we cover the FPCCD sensors. Section 2 introduces the FPCCD detector. Section 3 presents the status of the R&D. Section 4 summarizes the conclusions.

# 2. FPCCD Detector

# **Baseline Design Vertex Detector**

In order to reach performance level, the ILD vertex detector should comply with the following specifications:

- A spatial resolution near the IP better than 3  $\mu$ m

- A material budget below 0.15% X<sub>0</sub> /layer

- A first layer located at a radius of  $\approx 1.6$  cm

- A pixel occupancy not exceeding a few percent.

The power consumption should be low enough to minimize the material budget of the cooling system inside the detector sensitive volume.

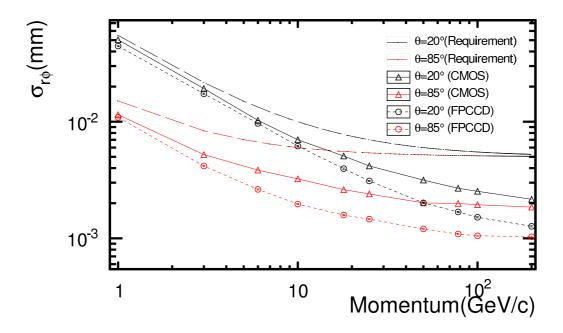

Simulations show that such resolution level is feasible with the proposed technologies (Fig. 1).

The baseline design of the ILD vertex detector consists of three, nearly cylindrical, concentric layers of double-sided ladders. Each ladder is equipped with pixel sensors on both sides,  $\approx 2$  mm apart, resulting in six measured impact positions for each charged particle crossing the detector (Fig. 2). The radii covered by the detector range from 16 mm to 60 mm. The material budget of each ladder amounts to  $\approx 0.3$  %  $X_0$ , equivalent to 0.15%  $X_0$ /layer.

This geometry is independent of the actual pixel technology being finally adopted.

<sup>&</sup>lt;sup>1</sup>The International Large Detector (ILD) [7] is a concept for a detector at the ILC.

**Figure 1:** Impact parameter resolution of the ILD vertex detector for two different particle production angles  $(20^{\circ} \text{ and } 85^{\circ})$ , assuming the baseline point resolution for the CMOS option (solid line), and the FPCCD option (dotted line). The curves with long dashes show the performance goal.

**Figure 2:** Schematic view of the ILD vertex detector. Every layer consists of three concentric layers of double-sided ladders. The inner layer length in the beam direction is half of the outer layers.

# **FPCCD**

The FPCCD concept is based on the following:

- 1. Very small pixel size ( $\approx 5 \mu \text{m}$ ).

- 2. Fully depleted sensitive volume with 15  $\mu$ m epitaxial layer thickness.

- 3. Readout between consecutive bunch trains crossing the interaction point.

The first item provide FPCCD detector with excellent impact parameter resolution, below 1.4  $\mu$ m, at high momentum limit for tracks with polar angle 90 degree.

The second item imply the charge spread between pixels is very small.

Readout in the inter-train has the additional advantage that the FPCCD is intrinsically free of beam-induced RF noise.

Another advantage of using FPCCD, and an unique feature of this sensor technology, it is use the cluster shapes to the beam-induced backgrounds [3].

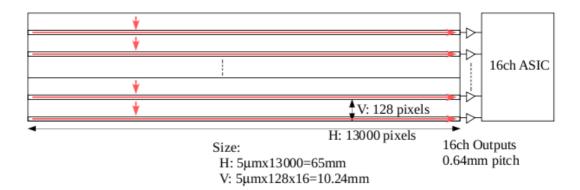

**Figure 3:** Schematic view of the innermost ladder of the FPCCD sensor. Each CCD wafer has 16 outputs covering 16 regions, and each region has 128 (V) x 13000 (H) pixels. Each region has a horizontal register to transfer the signal charge to the output node.

The main relevant background stems from e<sup>+</sup>e<sup>-</sup> pairs from beamstrahlung which are produced in the highly charged environment of the beam-beam interaction.

Schematic design of the FPCCD sensor is shown in Figure 3. The pixel size is 5  $\mu$ m square and the thickness of the sensitive layer is 15  $\mu$ m. For the outer layers, the pixel size could be somewhat larger. Each CCD wafer has 16 outputs covering 16 regions, and each region has 128 (V) x 13000 (H) pixels. The reason why the number of vertical (V) transfer is much less than the number of horizontal (H) transfer is that this configuration is more advantageous for the radiation tolerance. Each region has a horizontal register to transfer the signal charge to the output node. Pixels in the horizontal registers are also sensitive to the charged particles.

The required frequency to read out the whole pixels with this configuration is  $\approx 10$  Mpixels/s.

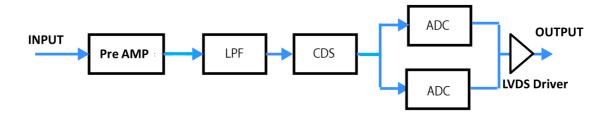

The output signals from one edge of the CCD wafer are processed by an ASIC located next to the CCD wafer. This ASIC will have functions of amplifier, low-pass filter, correlated double sampler, and analog-to-digital converter (ADC) for 16 channels (Fig. 4).

# 3. Status R&D on FPCCD

**Small Prototype Tests**

**Figure 4:** Readout ASIC overall architecture. ASIC has functions of amplifier, low-pass filter (LPF), correlated double sampler (CDS) and analog-to-digital converter (ADC). Two ADC are used to achieve the required readout speed.

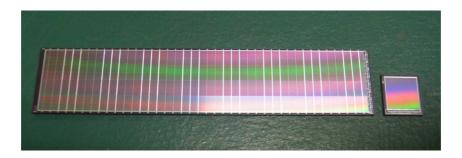

**Figure 5:** Small and full size prototype sensor with 6  $\mu$ m pixel size.

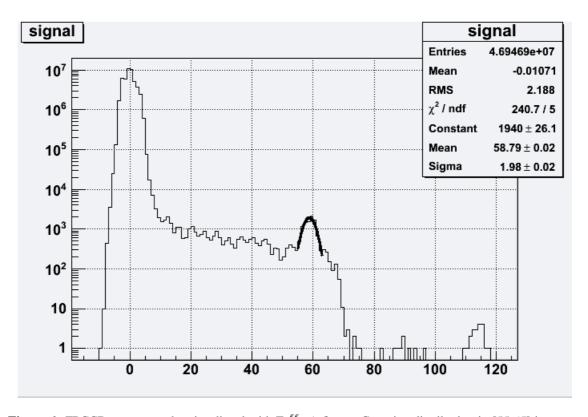

We have made small prototype sensors with 6  $\mu$ m pixel size and full size prototypes for the inner layers (Fig. 5). The readout system has been developed with 3 front-end ASIC'S prototypes already fabricated. The last ASIC prototype matches most of the design requirements [5] when operating at frequencies lower than 50 MHz. At high frequency (100 MHz) it is observed one increase in the noise of the readout system. Figure 6 shows the sensor response when irradiated with Fe<sup>55</sup>.

We estimate the amount of noise as 60 electrons, which is not far from the required value for FPCCD (50 electrons). The main noise contribution is CCD readout circuit.

# Software R&D

We have developed a new vertex tracking, FPCCD Track Finder [6].

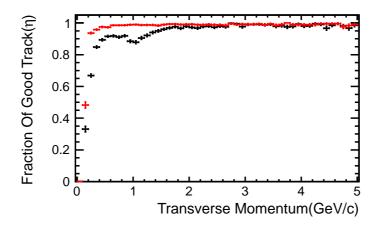

The new track finder tracking efficiency is  $\approx$  99% for  $p_T > 0.6$  GeV/c. Figure 7 shows the improve in the tracking efficiency for low  $p_T$  tracks when using FPCCD.

We have found that using a bigger pixel size (10  $\mu$ m) in the outer layers saves  $\approx$  30 % power consumption with no impact on the performance [6].

Figure 6: FPCCD response when irradiated with  $Fe^{55}$ . A fit to a Gaussian distribution in [55,65] is superimposed.

Figure 7: Comparison FPCCD Track Finder (red) with previous vertex tracking [7] (black).

# 4. Conclusion

Fine pixel CCD (FPCCD) is one of the three sensor technologies being actively developed for the ILD vertex detector. We have cover the status of the R&D in the FPCCD detector. The tests carried out on the small prototypes match the design requirements on noise level and power consumption at low frequency (< 50 MHz).

We have developed a new Silicon Tracking, FPCCD Track Finder, which improves tracking efficiency on low  $p_T$  tracks.

We have found that using pixel sizes of  $10 \ \mu \text{m}^2$  in the outer layers reduce 30% the power consumption while keeping similar  $d_0$  resolution and occupancy.

We are analyzing the Charge Transfer Inefficiency (CTI) for the FPCCD. We plan to perform a beam test to study the radiation hardness of the sensors.

# References

- [1] Y. Sugimoto, et al., CCD-based vertex detector for GLC, Nucl. Instrum. Meth. A549, 87-92, 2005.

- [2] Y. Sugimoto, Fine Pixel CCD Option for the ILC Vertex Detector, Proceedings of International Linear Collider Workshop, Stanford, California, 18-22 Mar. 2005, 550-554.

- [3] Y. Sugimoto, et al., FPCCD Vertex Detector R&D for ILC, [arXiv:1202.5832 physics.ins-det]

- [4] K. Abe, et al., Nucl. Instrum. Meth. A400 (1997) 287.

- [5] E. Kato, et al., Development of readout ASIC for FPCCD vertex detector at the ILC, [http://ieeexplore.ieee.org/xpl/articleDetails.jsp?arnumber=6551171]

- [6] Performance Evaluation and Software Development of FPCCD Vertex Detector in ILC, ECFA LC2013.

- [7] T. Behnke, J. E. Brau, P. N. Burrows, J. Fuster, M. Peskin, et al., *The International Linear Collider Technical Design Report Volume 4: Detectors*, [arXiv:1306.6329 physics.ins-det].